PAM-XIAMEN offers GaN on silicon HEMT wafer for Power, E-mode. Because the normally-on characteristic will Increase the complexity of circuit design and power consumption, designing an enhanced (E-Mode) HEMT that is turned off under zero grid bias will be crucial for advancing the application of GaN-on-Silicon HEMT in the power field.

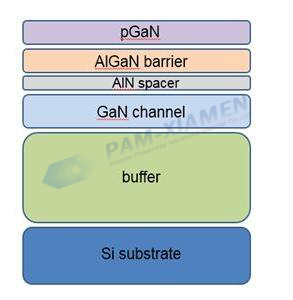

1. Structures of E-MODE GaN HEMT on Silicon Substrate

No. 1 GaN on Silicon Epitaxial HEMT Structure

| GaN on silicon HEMT epitaxy size | 2″, 4″, 6″,8″ |

| AlGaN/GaN HEMT structure | Refer 1.2 |

| Residual 2DEG density (Vg=0 V) | <1e18/cm3 |

| AFM RMS (nm)of 5x5um2 | <0.25nm |

| Bow(um) | <=30um |

| Edge exclusion | <5mm |

| p-GaN | / |

| u-GaN cap layer | / |

| Al composition | 20-30% |

| AlGaN barrier layer | / |

| GaN channel | / |

| AlGaN buffer | / |

| Substrate material | Silicon substrate |

| Si wafer thickness (μm) | 675um(2″), 1000um(4″), 1300um(6″), 1500um(8″) |

No. 2 4-inch GaN / Si Epi-Wafer PAM200211-HEMT

| GaN / Si HEMT Epi Structure | ||

| Layer | Material | Thickness |

| 6 | p-GaN, Mg-doped | – |

| 5 | AlN | – |

| 4 | AlGaN | – |

| 3 | AlN | – |

| 2 | GaN (channel layer) | – |

| 1 | Buffer (Al,Ga)N | > = 4 um |

| Substrate | Si (111), 1000+/-25um thick, deflection <10 um | |

Remark:

1/ At present, our standard structure AlGaN 12NM, 25% Al has the corresponding parameter carrier concentration > 6e12, mobility > 2000, RS ~ 500, much better;

2/ The current Mg doping concentration is ~ 2e19 and the activation concentration is ~ 4e17.

Features of GaN on Si Epiwafers for power:

High uniformity and good repeatability;

Low leakage current with excellent;

2DEG transport properties;

Breakdown voltage ≥ 650 V;

RoHS compliant

Typical Applications of Si based GaN Epiwafers:

Suitable for power HEMTs and low cost CMOS process;

Suitable for power diodes

2. What is E Mode GaN on Silicon HEMT?

Changing the process structure of the GaN on silicon HEMT gate to switch the threshold voltage polarity can produce an enhanced (E-type) GaN HEMT device. The purpose of the process structure change is to deplete the 2DEG under the gate with the condition of no applied voltage, so that the forward threshold voltage can be enhanced by the 2DEG to form a channel. P-doped GaN gate is a structure similar to a diode in the gate structure, and the threshold voltage is raised by the diode voltage drop.

Currently, there are three main methods for using p-type gate to realize GaN-based enhanced mode HEMT:

- The first method of p-type gate is mainly to use the entire epitaxial p-type layer on the barrier layer, and then etch and retain the p-type layer under the gate to realize the enhancement;

- The second is to trim the p-type epitaxial layer, then retain the p-type layer under the gate, and etch most of the p-type layer in the non-gate area, leaving 5-20 nanometers of the p-type layer. During the etching process, plasma will damage the interface and affect the stability of the GaN on silicon power device;

- The third method of p-type gate is to do secondary epitaxy in the gate area on the barrier layer to grow the p-type gate.

3. FAQ about GaN on Si Wafer for Power, E-mode

Q1: About the surface treatments for E-mode GaN on Si HEMT wafer: would you also give us some hints to overcome this hard problem? Especially gate process is in our minds. We are not very sure about the treatments before gate metal evaporation.

A: Concerning the surface of GaN on Si HEMT wafer, organic treatments are important after the pGaN etching, to repair the etched surface.

Q2: For the GaN on Si epi structure for E-mode HEMT, we also performed some simulations and achieved similar results in simulations. I mean 13nm of AlGaN barrier will be good for the expected Vth value. You can obtain 180mA/mm but at which DS distance you observe this current density?

According to our simulations decreasing the AlGaN thickness to 13nm is good but to be safe we also need to keep the Al mole fraction at 0.18. Do you have any predictions how much this will change the IDSS?

A: Our source to drain distance is ~25 μm based on the HEMT epitaxial structure. Concerning the Idss of 13 nm Al(0.18) GaN barrier, it is difficult to say, as it is also influenced by the etching accuracy. For your reference, we have worked on a device with 12 nm Al(0.15)GaN barrier, the Idss is ~72 mA/ mm.

Q3: About GaN-on-Si based devices with the threshold voltage, we have tried different gate metals (Pd, tungsten, Ni, NiAu, Ti, etc) but it is always 0.7V. We need to increase it up to 1.2V do you also have some recommendations about this problem? Your guidance will help too much.

A: Concerning the breakdown voltage (BV): Wafers with the same/similar epi structure of GaN/Si HEMT is always processing in our own fab, and a stable BV output is obtained, with BV >650 V (Ieakage current Ids < 1 μA). A higher BV should be achieved by proper surface treatments and optimized passivation layer.

Q4: We are thinking to modify the AlGaN thickness of GaN HEMT structure to increase the Vth. What do you think? Or maybe you can suggest some other things to increase the Vth.

A: Concerning the threshold voltage Vth of E-mode GaN/Si HEMT wafer: We believe the Vth can be enhanced by reducing the barrier thickness. We can obtain devices with Vth >1.5 V easily in our fab, with a ~13 nm Al0.2Ga0.8N barrier, while a relative high on state current can still be maintained (>180 mA/ mm). In your case, the AlGaN barrier is a bit thicker (18 nm), which may limit the Vth values to be < 1 V.

Q5: Do we need any kind of activation for Mg doping or did you already activated the doping in HEMT wafer of GaN on Si?

A: We already activated the doping in GaN-on-Si HEMT wafer.

Q6: We are still working on optimizing the process on your wafer. Till now we were able to achieve 420 V breakdown with the PGaN E mode wafer.

What is your estimation about breakdown voltage? How high we can go? I remember that you’ve told me that 650V may be abit difficult with E mode.

Do you have some progress on epi growth in the mean time? Is it possible to purchase a D mode wafer with 650V breakdown?

A: The breakdown voltage can reach to 1000V for both D mode and E mode HEMT wafer.

Q7: I remember that the vertical breakdown can go up to 1000V and we also measured about 900V with one of the samples. For the 600v operation you’ve suggested D mode. I understand that E mode will not be able to reach that value. Am I mistaken? Do you have any hints for us for achieving 600V by E mode wafers?

A: In 600v operation, we suggest use D mode HEMT wafer, which is more suitable in this voltage, but it doesn’t mean that breakdown voltage only reach to 600v, as mentioned, both can reach to 1000v.

Q8: Currently we are working on improving the breakdown voltage of the devices with your GaN on Si HEMT wafer. We obtained ~350V but we are searching the ways to reduce the leakages to improve the breakdown. But in the mean time we have problem with the threshold voltage. We need to have more positive voltages. I need your help and suggestions to improve the results.

What I have in mind is to decrease the AlGaN barrier thickness a bit but compensating the Ns loss with increasing the Al composition just a bit. In our opinion this should improve the threshold voltage of the devices. What do you think? We may order another wafer to improve these parameters.

Do you have any suggestions to improve the breakdown voltage of the device?

A: RE: the breakdown voltage of HEMT devices on GaN/Si wafer:

The wafer we have delivered to you is based on our HV buffer, which has a vertical breakdown voltage > 1000 V (@I < 1 uA/ mm2).

Actually, according to the devices fabricated on this epi structure, in our own fab, the off state leakage is Ids< 0.1 uA/ mm, while Vds = 650 V (Lds=15 um).

Both epi buffer and chip process contribute to the leakage, so we suggest you to check the chip process, especially the passivation layer, which is also critical for the leakage.

RE: the Vth of devices on GaN on Silicon HEMT wafer:

A thinner barrier layer will help increase the Vth for sure.

we can reduce the AlGaN (20% Al) thickness to 12.5 nm for you (the previous one was ~ 18 nm).

A Vth> 2 V (@Ids~10 uA/ mm) has been demonstrated in our fab, based on this structure.

Although it will sacrifice the Rs, a Rs value of ~550 ohm/sq is obtained.

By the way, the chip process, especially gate material, is also important for Vth.

Q9: I appriciate your reply. Thank you. We don’t face a problem with vertical breakdown we also measure about 1kV. But the DS leakage (we use LDS12um) is higher and we cannot achieve 650V.

To my observation our main problem comes from the gate leakage. And as you’ve stated gate material affects this leakage. We use Ni/Au as gate metal. But your little guidance will be much appriciated. What may be your suggestion to improve the gate leakage and the Vth as well? Do you use ALD or similar dielectric under the gate metal? Which metal structure do you use? What kind of things do you suggest to improve the gate contact?

A: RE: the gate metal for GaN HEMT device fabrication:

Our production line is “Au” free, so no Au is used, and also, Ni/Au contact usually gives high gate leakage.

Three types of gate contact may improve Vth: Ni, W (wolfram), or TiN (our option).

Concerning the leakage:

We measure the off state leakage at Vg = 0 V.

Actually, it depends on the Vth, if your Vth is close to 0 V, leakage at Vg=0V is high, as the device is not complete “turn off”; if the Vth > 1.5 V, our device gives low leakage (sub uA) @ Vg = 0 V.

Please be careful with the etching defects, which may also contribute to the off state leakage.

We hope the above information can help.

Q10: I would like to insert an 1 nm AlN layer between p-GaN and AlGaN. Is it possible?

A: No problem to inser an 1nm AlN layer between p-GaN and AlGaN, but which can not help to stop etch.

For more information, please contact us email at victorchan@powerwaywafer.com and powerwaymaterial@gmail.com.