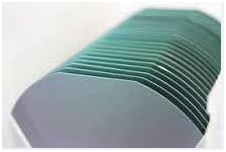

PAM-XIAMEN can offer 4 inch test grade silicon wafer with single side polished. The parameters for 4″-SSP Si wafer at test grade are as follows:

1. Parameters of Si Single Crystal Wafer at Test Grade

PAM-210310-Si wafer

| Sl No | Item | Specifications |

| 1 | Growing Method | CZ |

| 2 | Wafer Diameter | 100±0.5 mm |

| 3 | Wafer Thickness | 525±25 μm |

| 4 | Wafer Surface Orientation | <100>±0.5º |

| 5 | Type | P type |

| 6 | Dopant | Boron |

| 7 | Dislocation Density | Less than 5000/cm2 |

| 8 | Resistivity | 2-8 Ohm-cm |

| 9 | Radial Resistivity Variation(max.) | N/A |

| 10 | Flatness | |

| 10a | BOW(max.) | 50 μm |

| 10b | TIR | N/A |

| 10c | TTV | 10 μm |

| 10d | WARP | N/A |

| 11 | Primary Flat | |

| 11a | Length | 32.5±2.5 mm |

| 11b | Orientation | (110)±0.2º as per SEMI Standard |

| 11c | Secondary Flat | As per SEMI Standard |

| 12 | Front Surface Finish | Mirror Polished |

| 13 | Max. particles of size ≥0.3μm | < 30pcs |

| 14 | Scratches, Haze, Edge Chips, Orange Peel&Other defects | N/A |

| 15 | Back Surface | Etched |

| 16 | Packing Requirement | wafer cassette |

2. Future Development of Test Grade Silicon Wafer

High-purity single crystal silicon is an important semiconductor material. A p-type silicon semiconductor can be formed by adding a small amount of group IIIA elements to the monocrystalline silicon; a small amount of group VA elements are added to form an n-type semiconductor. The p-type semiconductor and the n-type semiconductor are combined to form a p-n junction. In addition, the diodes, triodes, thyristors, field effect transistors and various integrated circuits (including chips and CPUs in computers) are all made of silicon. Silicon wafer test grade is a promising material in the development of energy.

Currently, the photovoltaic industry is still dominated by P-type silicon wafers. P-type silicon wafers are doped with boron. The segregation coefficient of boron and silicon is equivalent, and the dispersion uniformity is easy to control. Therefore, the manufacturing process is simple, and the cost is lower, but the highest efficiency has a limitation. N-type silicon wafers are doped with phosphorus, and the compatibility of phosphorus with silicon is poor. The distribution of phosphorus is uneven when the rod is drawn, and the process is more complicated. However, the N-type test grade silicon wafer usually has a longer lifespan, and the battery efficiency can be higher. The improvement of efficiency refers to the improvement of photoelectric conversion efficiency. So in the future, the technological development of silicon wafers is mainly based on improving efficiency and reducing costs.

For more information, please contact us email at victorchan@powerwaywafer.com and powerwaymaterial@gmail.com.