SiC Epitaxy

- Description

Descrizione del prodotto

SiC epitassia

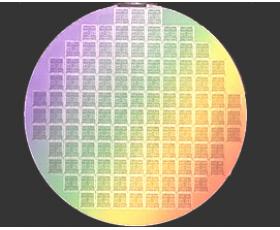

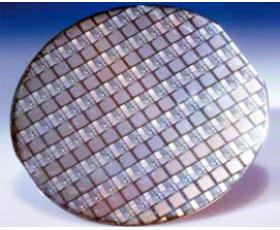

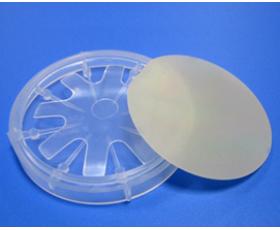

PAM-XIAMEN provide custom thin film (silicon carbide) SiC epitaxy on 6H or 4H substrates for the development of silicon carbide devices. SiC epi wafer is mainly used for the fabrication of 600V~3300V power devices, including SBD, JBS, PIN, MOSFET, JFET, BJT, GTO, IGBT, etc. With a silicon carbide wafer as a substrate, a chemical vapor deposition (CVD) method is usually used to deposit a layer of single crystal on the wafer to form an epitaxial wafer. Among them, SiC epitaxy are prepared by growing silicon carbide epitaxial layers on conductive silicon carbide substrates, which can be further fabricated into power devices.

1.Specifica dell'epitassia SiC:

| Elementi | Specificazione | Valore tipico |

| Poly-type | 4H | — |

| Off-orientamento verso | 4 gradi di spegnimento | — |

| <11 2_ 0> | ||

| Conduttività | tipo n | — |

| drogante | Azoto | — |

| Concentrazione Carrier | 5E15-2E18 cm-3 | — |

| Tolleranza | ± 25% | ± 15% |

| Uniformità | 2”(50,8 mm) < 10% | 7% |

| 3" (76,2 mm) < 20% | 10% | |

| 4" (100 mm) < 20% | 15% | |

| Gamma di spessori | 5-15 micron | — |

| Tolleranza | ± 10% | ± 5% |

| Uniformità | 2”< 5% | 2% |

| 3”< 7% | 3% | |

| 4”< 10% | 5% | |

| Difetti di punta di grandi dimensioni | 2”< 30 | 2”< 15 |

| 3”< 60 | 3”< 30 | |

| 4”< 90 | 4”< 45 | |

| Difetti epi | 20 cm-2 | 10 cm-2 |

| Grappolo a gradini | 2.0nm (Rq) | 1.0nm (Rq) |

| (Rugosità) |

Esclusione del bordo di 2 mm per 50,8 e 76,2 mm, esclusione del bordo di 3 mm per 100,0 mmNote:

• Media di tutti i punti di misurazione per lo spessore e la concentrazione del vettore (vedi pag. 5)

• Gli strati epi di tipo N <20 micron sono preceduti da uno strato tampone di tipo n, 1E18, 0,5 micron

• Non tutte le densità di drogaggio sono disponibili in tutti gli spessori

• Uniformità: deviazione standard (σ)/media

• Eventuali requisiti speciali sull'epi-parametro sono su richiesta

2. Introduzione dell'epitassia SiC

Perché abbiamo bisogno del wafer epitassiale in carburo di silicio? Poiché diversi dal tradizionale processo di produzione dei dispositivi di alimentazione al silicio, i dispositivi di alimentazione al carburo di silicio non possono essere fabbricati direttamente su materiali monocristallini in carburo di silicio. I materiali epitassiali di alta qualità devono essere coltivati su substrati monocristallini conduttivi e vari dispositivi prodotti sul wafer epitassiale di SiC.

La principale tecnologia epitassiale per la crescita dell'epitassia di SiC è la deposizione chimica da vapore (CVD), che realizza un certo spessore e materiale epitassiale di carburo di silicio drogato attraverso la crescita del flusso a gradini del reattore di epitassia SiC. Con il miglioramento dei requisiti di produzione dei dispositivi di alimentazione in carburo di silicio e la resistenza ai livelli di tensione, il wafer SiC epi continua a svilupparsi nella direzione di difetti bassi e epitassia spessa.

Negli ultimi anni, la qualità dei materiali epitassiali sottili in carburo di silicio (<20 μm) è stata continuamente migliorata. I difetti dei microtubuli nei materiali epitassiali sono stati eliminati. Tuttavia, i difetti dell'epitassia SiC, come goccia, triangolo, carota, dislocazione della vite, dislocazione del piano basale, difetti di livello profondo, ecc., Diventano il fattore principale che influenza le prestazioni del dispositivo. Con l'avanzamento del processo di epitassia SiC, lo spessore dello strato epitassiale si è sviluppato da pochi μm e decine di μm in passato alle attuali decine di μm e centinaia di μm. Grazie ai vantaggi del SiC rispetto al Si, il mercato dell'epitassia del SiC sta crescendo rapidamente.

Poiché i dispositivi in carburo di silicio devono essere fabbricati su materiali epitassiali, fondamentalmente tutti i materiali monocristallini in carburo di silicio verranno utilizzati come film epitassiale di SiC per coltivare materiali epitassiali. La tecnologia dei materiali epitassiali in carburo di silicio si è sviluppata rapidamente a livello internazionale, con lo spessore epitassiale più elevato che raggiunge più di 250 μm. Tra questi, la tecnologia dell'epitassia di 20 μm e inferiore ha un'elevata maturità. La densità del difetto superficiale è stata ridotta a meno di 1/cm2 e la densità della dislocazione è stata ridotta da 105/cm2 a 103/cm2. Il tasso di conversione della dislocazione del piano di base è vicino al 100%, il che ha sostanzialmente soddisfatto i requisiti dei materiali epitassiali per la produzione su larga scala di dispositivi al carburo di silicio.

Negli ultimi anni, anche la tecnologia internazionale dei materiali epitassiali da 30 μm~50 μm è maturata rapidamente, ma a causa della limitazione della domanda del mercato epi di SiC, il progresso dell'industrializzazione è stato lento. Al momento, l'azienda di industrializzazione può offrire materiali epitassiali in carburo di silicio in lotti, tra cui epitassia Cree SiC, epitassia PAM-XIAMEN SiC, epitassia Dow Corning SiC ecc.

3. Metodi di prova

n.1. Concentrazione del vettore: il doping netto è determinato come valore medio attraverso l'afer utilizzando la sonda Hg CV.

n.2. Spessore: lo spessore è determinato come valore medio attraverso il wafer utilizzando FTIR.

No.3. Difetti di grandi dimensioni: ispezione microscopica eseguita a 100X, su un microscopio ottico Olympus o comparabile.

n.4. Ispezione dei difetti epi o mappa dei difetti eseguita sotto KLA-Tencor Candela CS20 Optical Surface Analyzer o SICA.

n.5. Raggruppamento a gradini: Il raggruppamento a gradini e la rugosità vengono scansionati da AFM (microscopio a forza atomica) su un'area di 10μm x10μm

3-1:Descrizioni dei difetti dei punti grandi

Difetti che mostrano una forma chiara all'occhio non assistito e sono > 50 micron di diametro. Queste caratteristiche includono punte, particelle aderenti, schegge e crateri. Difetti di grandi dimensioni a meno di 3 mm di distanza contano come un difetto.

3-2: Descrizioni dei difetti dell'epitassia

I difetti dell'epitassia SiC includono inclusioni 3C, code di comete, carote, particelle, goccioline di silicio e caduta.

4. Applicazione di wafer epitassiale SiC

Rifasamento (PFC)

Inverter fotovoltaici e inverter UPS (alimentazione continua)

Azionamenti a motore

Rettifica dell'uscita

Veicoli ibridi o elettrici

È disponibile un diodo SiC Schottky con 600V, 650V, 1200V, 1700V, 3300V.

Si prega di vedere sotto il dettaglio dell'applicazione per campo:

| Campo | Radiofrequenza (RF) | Dispositivo di alimentazione | GUIDATO |

| Materiale | SiLDMOS | Si | GaN/Al2O3 |

| GaAs | GaN/Si | GaN/Si | |

| GaN/SiC | SiC/SiC | GaN/SiC | |

| GaN/Si | Ga203 | / | |

| Dispositivo | SiC GaN HEMT | MOSFET a base di SiC BJT . basato su SiC IGBT . basati su SiC SBD . a base di SiC |

/ |

| Applicazione | Radar, 5G | Veicoli elettrici | Illuminazione a stato solido |

5. Wafer meccanici con strati Epi: sono disponibili, ad esempio per il monitoraggio dei processi, che richiedono wafer con arco e deformazione bassi.

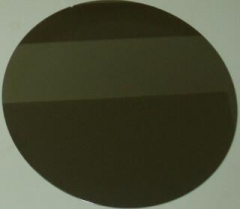

150 millimetri 4H n wafer di tipo SiC EPI

Epistrato di SiC intrinseco su substrato di carburo di silicio

Perché abbiamo bisogno del wafer epitassiale in carburo di silicio?

Struttura MOSFET SiC omoepitassiale su substrato SiC

Film sottile epitassiale di carburo di silicio (SiC) per rilevatori