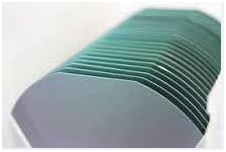

PAM-XIAMEN può offrire wafer di silicio di grado di prova da 4 pollici con un lato lucido. I parametri per wafer Si 4 ″ -SSP al grado di prova sono i seguenti:

1. Parametri di Si Single Crystal Wafer al grado di prova

Wafer PAM-210310-Si

| Sl No | Voce | Specificazioni |

| 1 | Metodo di coltivazione | CZ |

| 2 | Wafer Diametro | 100 ± 0,5 mm |

| 3 | Wafer Spessore | 525 ± 25 μm |

| 4 | Wafer orientamento della superficie | <100> ± 0,5º |

| 5 | Tipo | Tipo P. |

| 6 | drogante | Boro |

| 7 | lussazione Densità | Meno di 5000 / cm2 |

| 8 | resistività | 2-8 Ohm-cm |

| 9 | Variazione della resistività radiale (max.) | N / A |

| 10 | pianura | |

| 10a | ARCO (max.) | 50 μm |

| 10b | TIR | N / A |

| 10c | TTV | 10 μm |

| 10d | ORDITO | N / A |

| 11 | primaria piatto | |

| 11 bis | Lunghezza | 32,5 ± 2,5 mm |

| 11b | Orientamento | (110) ± 0,2º secondo lo standard SEMI |

| 11c | secondaria piatto | Come da standard SEMI |

| 12 | Finitura di superficie anteriore | specchio lucidato |

| 13 | Max. particelle di dimensioni ≥0.3μm | <30 pezzi |

| 14 | Graffi, foschia, patatine ai bordi, buccia d'arancia e altri difetti | N / A |

| 15 | superficie posteriore | Inciso |

| 16 | requisito di imballaggio | cassetta wafer |

2. Future Development of Test Grade Silicon Wafer

Il silicio monocristallino di elevata purezza è un importante materiale semiconduttore. Un semiconduttore di silicio di tipo p può essere formato aggiungendo una piccola quantità di elementi del gruppo IIIA al silicio monocristallino; una piccola quantità di elementi VA del gruppo viene aggiunta per formare un semiconduttore di tipo n. Il semiconduttore di tipo p e il semiconduttore di tipo n sono combinati per formare una giunzione pn. Inoltre, i diodi, i triodi, i tiristori, i transistor ad effetto di campo e vari circuiti integrati (inclusi chip e CPU nei computer) sono tutti realizzati in silicio. Il grado di prova del wafer di silicio è un materiale promettente nello sviluppo dell'energia.

Attualmente, l'industria fotovoltaica è ancora dominata dai wafer di silicio di tipo P. I wafer di silicio di tipo P sono drogati con boro. Il coefficiente di segregazione di boro e silicio è equivalente e l'uniformità di dispersione è facile da controllare. Pertanto, il processo di produzione è semplice e il costo è inferiore, ma la massima efficienza ha una limitazione. I wafer di silicio di tipo N sono drogati con fosforo e la compatibilità del fosforo con il silicio è scarsa. La distribuzione del fosforo non è uniforme quando l'asta viene estratta e il processo è più complicato. Tuttavia, il wafer di silicio per test di tipo N di solito ha una durata maggiore e l'efficienza della batteria può essere maggiore. Il miglioramento dell'efficienza si riferisce al miglioramento dell'efficienza di conversione fotoelettrica. Quindi, in futuro, lo sviluppo tecnologico dei wafer di silicio si basa principalmente sul miglioramento dell'efficienza e sulla riduzione dei costi.

Per ulteriori informazioni, contattaci tramite e-mail all'indirizzo victorchan@powerwaywafer.com e powerwaymaterial@gmail.com.