ほとんどのSiC電子デバイスは、昇華成長ウェーハで直接製造されるのではなく、最初の昇華成長ウェーハの上に成長するはるかに高品質のエピタキシャルSiC層で製造されます。 十分に成長したSiCエピ層は、優れた電気的特性を備えており、バルク昇華成長したSiCウェーハ材料よりも制御性と再現性が高くなっています。 したがって、高品質のエピ層の制御された成長は、有用なSiCエレクトロニクスの実現において非常に重要です。 大手エピタキシャルウェーハメーカーの1つとして、PAM-XIAMENはSiCエピタキシーSiC基板上。 詳細な仕様は、以下のエピタキシャル膜を備えたSiCウェーハを例に取ってください。

1. Specification of SiC Epi Layer Structure PAMP16192-SIC

直径2インチのSiC

4H

半絶縁性

4度オフ

300-500umの厚さ

Si面

両面研磨、半絶縁の向きはC(0001)

エピタキシャル膜:

厚さ1um

意図的なドーピングはありません

マーク:

Si面またはカーボン面は、半絶縁性とは相対的ではありません。通常、Si面は研磨され、エピ対応です。 または、C(0001)方向と言いました。 また、半絶縁の場合、C(0001)が主流であり、すべての基板メーカーは4度ずれではなく軸上で行っています。

SiCウェーハ上で高品質のSiCエピタキシーを実行するには、4度のオフが必要です。

2.4H-SiCエピレイヤー用のパラメーター

これまでに発表された最低の電子濃度は約1E14cmです3。 通常、層にさらに多くの表面欠陥を生成する特別な成長パラメータが必要です。

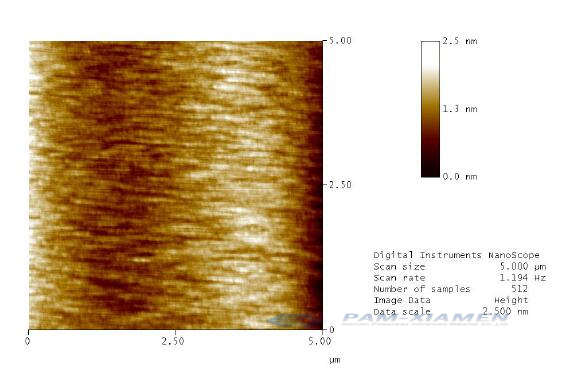

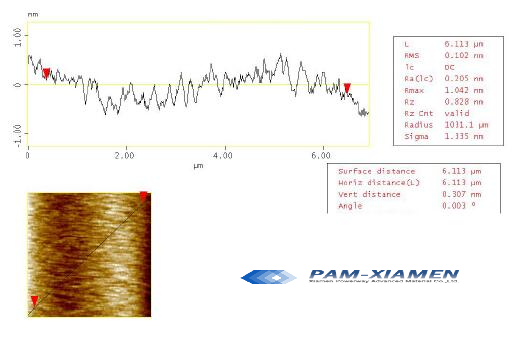

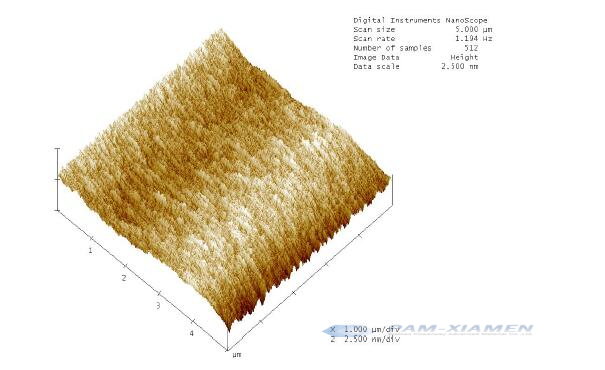

CV(キャリア濃度)を測定し、最も一般的な方法で抵抗率を計算します。 のために付属のAFMドープされていないSiCエピフィルムの濃度は1E15cmでした3.

3.SiC基板とエピ層のドーパント

上記の半絶縁性SiC基板上のSiCエピタキシャル層の仕様について、顧客からの大きな懸念の1つは、窒素、バナジウム、またはその他のドーパントを意図せずに組み込むと、エピタキシャル成長中にウェーハエピ層、バッファ層がn型になることです。

実際には、基板が半絶縁性であるため、バッファ層は必要ありません。これはホモエピタキシー(SiC上のSiC)です。 ドープされていない基板の方が優れていますが、バナジウムの場合でも機能します。 SiCの拡散係数は非常に低いです。 その上、不純物としての窒素は常にドープされていないエピSiCに存在し、層は常にn型です。 問題は、どれだけドープされているかです。 そして、表面/結晶を劣化させることなく、可能な限り低くなることを保証できます。

4.SiCエピウェーハの表面の特性評価

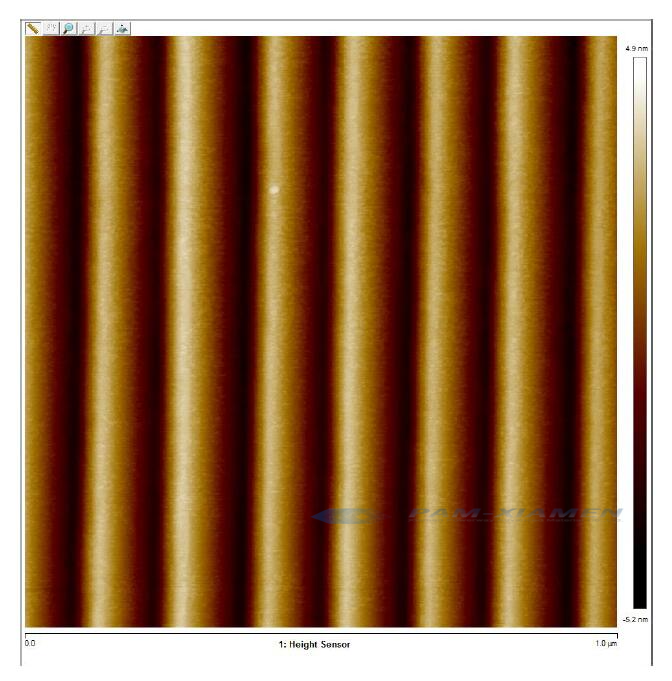

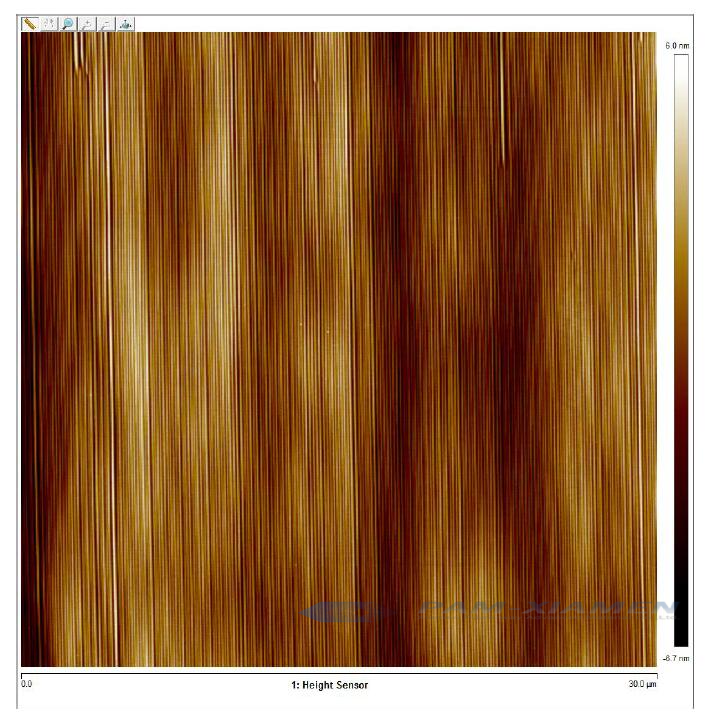

上のAFM画像を通して観察すると、隆起のある表面は非常に粗く見えます。これは、ステップバンチングが原因です。 ステップバンチングは常に存在しますが、ステップの高さを一定の範囲で制御できます。 これは、レイヤーの構造品質を向上させたい場合の例です。 SiC基板の粗さは、研磨後は常に低くなりますが、そのような表面の構造(結晶)品質は非常に低くなります。 優れたデバイスを作成する場合、ステップバンチング効果は「必要」であり、デバイスのパフォーマンスには影響しません。 たとえば、グラフェンの成長には10nmの粗さを使用します。 参考までに別のAFM結果を添付しました。

特定の目的では、滑らかなエピレイヤーがより重要です。 SiCエピ層の粗さには、ステップバンチングに接続されたマイクロステップとマクロステップの2つのパラメーターが含まれます。 エピウェーハ製造プロセスの2つのパラメータを制御して、エピ層の表面をより滑らかにし、ニーズに対応します。

詳細については、メールでお問い合わせください。 victorchan@powerwaywafer.com と powerwaymaterial@gmail.com.