PAM-Xiamen は、集積光導波路デバイスを製造するためのシリコンのエピタキシー ウェーハを提供できます。 当社が提供するシリコンエピウェーハは、Si基板上にコア層をSi、下部クラッド層をSiO2で成長させ、導波路構造をリッジ構造にしたものです。 Si と SiO2 材料の屈折率差が大きいため、この構造は光を最上層のシリコン構造に閉じ込めることができ、小型でコンパクトな光導波路デバイスを容易に得ることができます。 のより多くのパラメータシリコンエピウェーハ、次のように表を表示してください。

1. 集積導波路光学系用 Si エピタキシーウェーハの仕様

以下のシリコンウェーハエピタキシーは、通信波長範囲の集積導波路オプティクスのデバイスの製造に適しています。

PAM191012-SI

| パラメーター | 値 |

| 基板 | |

| ウェーハ材料 | 単結晶シリコン |

| ウェーハの大口径 | 100±0.2mm |

| 厚さ | ≥ 500um |

| 抵抗率 | >1 オーム * cm |

| 導電型 | – |

| 方向付け | – |

| ワーピング | ≤50um |

| ウェーハ曲げ | ≤50um |

| 例外エッジ | ≤5mm |

| 酸化層 | |

| レイヤー素材 | 酸化ケイ素 |

| 厚さ | 3.0±15um |

| ダッシュボード レイヤー | |

| レイヤー素材 | 単結晶シリコン |

| 厚さ | 120±10nm |

| 導電率タイプ | p/B またはドーピングなしの自己コンダクタンス |

| 結晶方位 | (1-0-0) ±0.5° |

| 抵抗率 | ≥1000 オーム * cm |

| 表面処理 | 研磨 |

| 表面粗さ | ≦5A |

| 表面汚染(粒子数) | 0.3 の粒子が 50 個以下 |

2. 光導波路材料としてシリコンを選択する理由

光導波路を作るためにシリコン材料を選択する主な理由は次のとおりです。

1) シリコンの吸収係数曲線を図 1 に示します。1300 nm を超える波長でのシリコン材料の吸収係数は比較的小さい (<1e-5 /cm) ため、光はその中を透過します。そして本質的な損失は非常に小さいです。

![]()

Fig.1 シリコンの吸収係数

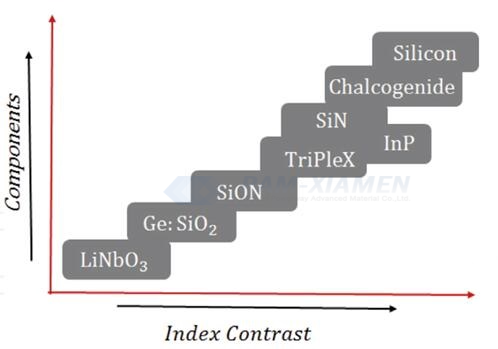

2) シリコンの屈折率は 3.48、二酸化ケイ素の屈折率は 1.44 であり、両者の屈折率のコントラストは 0.41 に達します (インデックスのコントラスト = (n1^2-n2^2)/2n1^2)。 したがって、光はシリコン導波路内でより適切に結合されます。 導波路のサイズが小さいほど、同じ面積の光チップにより多くの光デバイスを含めることができ、チップの集積度が高くなります。 図2は、異なる材料の一般的な光導波路の比較です。 シリコン エピタキシー ウェーハに基づく導波路は、デバイスの集積度が最も高いことがわかります。

図2 材質の異なる光導波路の比較

3) シリコン エピタキシャル フィルム ウエハーの処理は、導波路のエッチング、エピタキシー プロセス、またはドーピングのいずれであっても、比較的単純です。 シリコン導波路の製造プロセスは、大量生産に役立つCMOSプロセスと互換性があります。

3. 光導波路とは

光導波路は、光波を導波する媒体デバイスであり、媒体光導波路としても知られています。 光導波路には2つのタイプがあります。1つは、通常、オプトエレクトロニクス集積デバイス(またはシステム)の一部である、平面(薄膜)誘電体光導波路とストリップ形状の誘電体光導波路を含む統合光導波路です。 もう 1 つのタイプは、一般に光ファイバと呼ばれる円筒形の光導波路です。

そこでは、平面誘電体光導波路が最も単純な光導波路である。 これは、基板として屈折率 n2 のシリコン (またはガリウム砒素、またはガラス) を使用し、マイクロエレクトロニクス プロセスを使用して、屈折率 n1 の誘電体膜と屈折率 n3 のクラッド層でコーティングします。 . 通常、n1>n2>n3 を取ると、光波が誘電体膜内を伝播するように閉じ込められます。 ストリップ状の誘電体光導波路は、屈折率n2のマトリックス中に屈折率n1のストリップを生成し、n1>n2とし、ストリップ内を伝搬する光波を閉じ込める。 このような光導波路は、多くの場合、光スプリッタ、カプラ、スイッチ、およびその他の機能デバイスとして使用されます。

詳細については、メールでお問い合わせください。 victorchan@powerwaywafer.com と powerwaymaterial@gmail.com.