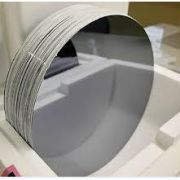

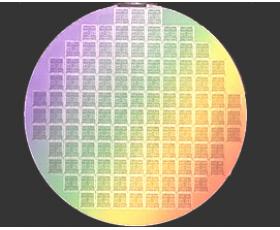

エピタキシャルシリコンウェーハ

シリコンエピタキシャルウェーハ(エピウェーハ)は、単結晶シリコンウェーハ上に堆積されたエピタキシャルシリコン単結晶の層です(注:高濃度にドープされた単結晶シリコンウェーハの上に多結晶シリコン層の層を成長させることもできますが、それはバルク Si 基板と最上部のエピタキシャル シリコン層の間にバッファ層 (酸化物またはポリ Si など) が必要であり、薄膜トランジスタにも使用できます。

- 説明

製品の説明

エピタキシャルシリコンウェーハ

シリコンエピタキシャルウェハ(エピウエハ)単結晶上に堆積されたエピタキシャル シリコン単結晶の層です。シリコンウエハ(注: 高ドープ単結晶シリコンウェーハの上に多結晶シリコン層を成長させることは可能ですが、バルク Si 基板と上部エピタキシャル層の間にバッファ層 (酸化物またはポリ Si など) が必要ですシリコン層であり、薄膜トランジスタにも使用できます。

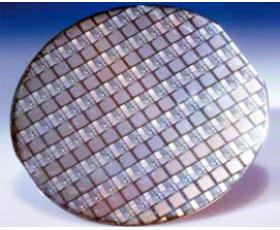

エピタキシャルシリコンウェーハの作製方法には、気相エピタキシー、液相エピタキシー、分子線エピタキシー等がある。 中でも、化学気相成長法 (CVD) をベースとした気相成長法がシリコンエピタキシャル成長プロセスの主流となっています。 一般的に使用されるソースは、SiCl4、SiHCl3、SiH2Cl2、SiH4 です。

さまざまな半導体デバイスのニーズを満たすために、エピタキシャルシリコンウェーハを製造するためのさまざまなシリコンエピタキシャル技術が生み出されてきました。 シリコンエピタキシャル成長には、低温エピタキシャル成長や減圧エピタキシャル成長のほかに、シリコンウェーハの特定の部分にシリコンエピタキシャル層を堆積させる選択エピタキシャル成長もあります。

基板の結晶構造を継続しながら、それが正確なドーピング濃度に、堆積されるエピタキシャル層をドープすることができます。

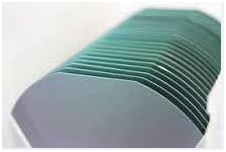

エピ層の抵抗:150オームcmへ<1オームセンチアップ

エピ層の厚さ:<1 umの150までのUM

構造:N / N +、N- / N / N +、N / P / N +、N / N + / P-、N / P / P +、P / P +、P- / P / P +。

ウエハアプリケーション:デジタル、リニア、パワー、MOS、BiCMOSのデバイス。

一目で私たちの利点

1.高度なエピタキシャル成長装置、テスト装置およびエピタキシャルシリコン技術。

低欠陥密度と良好な表面粗さを持つ最高品質2.Offer。

当社の顧客のための研究チームのサポートと技術サポートを3.Strong

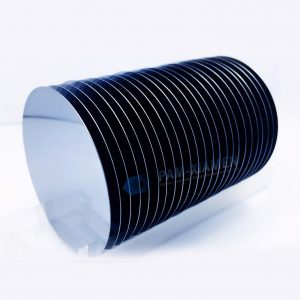

6」(150ミリメートル)ウェーハ仕様:

| アイテム | 仕様 | |

| 基板 | サブスペック号 | |

| インゴット成長方法 | CZ | |

| 導電型 | N | |

| ドーパント | として | |

| 方向付け | (100)が0.5°、±します | |

| 抵抗率 | ≤0.005Ohm.cm | |

| RRG | ≤15% | |

| [大井]コンテンツ | 8〜18 PPMA | |

| 直径 | 150±0.2ミリメートル | |

| プライマリフラット長 | 55〜60ミリメートル | |

| プライマリフラット場所 | {110}±1° | |

| 第二にフラット長 | セミ | |

| 第二にフラット場所 | セミ | |

| 厚さ | 625±15ええと | |

| 特性の裏側: | ||

| 1、BSD /ポリ-Si(A) | 1.BSD | |

| 2、SIO2 | 2.LTO:500 A±5000 | |

| 3、エッジ除外 | 3.EE:?0.6ミリメートル | |

| レーザーマーキング | 無し | |

| 前面 | 鏡面研磨 | |

| エピ | 構造 | N / N + |

| ドーパント | フォス | |

| 厚さ | 3±0.2μmの | |

| Thk.Uniformity | ≤5% | |

| 測定位置 | エッジから中心(1点)10ミリメートル(90度@ 4つのPTS) | |

| 計算 | 【のTmax-Tminを〕÷〔のTmax + Tminの] X 100% | |

| 抵抗率 | 2.5±0.2 Ohm.cm | |

| Res.Uniformity | ≤5% | |

| 測定位置 | エッジから中心(1点)10ミリメートル(90度@ 4つのPTS) | |

| 計算 | [さRmax-Rminの]÷[さRmax + Rminの] X 100% | |

| スタック欠陥密度 | ≤2(EA / cm 2)を | |

| ヘイズ | 無し | |

| 傷 | 無し | |

| クレーター、オレンジピール、 | 無し | |

| エッジクラウン | ≤1/ 3エピ厚さ | |

| スリップ(ミリメートル) | 全長≤1Dia | |

| 異物 | 無し | |

| 裏面の汚染 | 無し | |

| 合計点欠陥(粒子) | ≤30@0.3um |