우수한 전기적, 열적, 내방사성으로 인해 탄화규소는 고주파, 고전력 및 강력한 방사 환경에 응용할 수 있는 잠재적인 소재가 되었습니다. MOS 커패시터는 MOSFET의 기본 구조뿐만 아니라 반도체 표면과 인터페이스를 연구하는 중요한 수단입니다. 따라서 SiC MOS 커패시터에 대한 체계적인 연구는 SiC 기반 전자 장치의 내방사선성 향상과 장치의 수명 향상에 큰 의미가 있습니다. 선도적인 에피택셜 웨이퍼 제조업체 중 하나로서,PAM-하문MOS 커패시터용 SiC 에피 웨이퍼 제조 공정을 제공할 수 있습니다. 특정 매개변수는 다음 표를 참조하십시오.

1. 4HN SiC Epitaxial Wafer 사양

PAM210218 – MOSC

| SL 번호 | 사양 | |

| 1 | 웨이퍼 재료 | 4H-실리콘 카바이드 |

| 2 | 웨이퍼 구성 | 에피와 N+ |

| 3 | 에피 레이어 수 | 2개의 층 |

| 레이어 1: 버퍼 레이어 | ||

| 레이어 2: 최상위 레이어 | ||

| 4 | 레이어 2 두께 | 5/8/10um±10% |

| 5 | 레이어 2 도펀트 | 질소 |

| 6 | 두께 균일성 | <=5% |

| 7 | 표면 결함 밀도 | <1/센티미터2 |

| 8 | 레이어 2 도핑 농도 | 1.0 × 1016센티미터-3+/-20% |

| 9 | 농도 균일성 | <=10% |

| 10 | 레이어 1 두께 | 0.5um±10% |

| 11 | 레이어 1 도펀트 | 질소 |

| 12 | 레이어 1 도핑 농도 | 1.0 × 1018센티미터-3+/-50% |

| 13 | 전면 | 시페이스 |

| 14 | 기판 전도도 유형 | 강하게 도핑된 n-타입 |

| 15 | 도펀트 | 질소 |

| 16 | 결정 방향 | (0001)±0.25° |

| 17 | 오프 오리엔테이션 | <11-20> 방향으로 4° |

| 18 | 마이크로파이프 밀도 | ≤1cm-2 |

| 19 | 전기 저항 | 0.015~0.028옴-센티미터 |

| 20 | 직경 | 100±0.4mm |

| 21 | 두께 | 350±25 음 |

| 22 | TTV | ≤10 음 |

| 23 | LTV | ≤4 음 |

| 24 | 경사 | ≤35 음 |

| 25 | 기본 평면 방향 | <11-20> |

| 26 | 보조 평면 방향 | <1-100> |

| 27 | Si-페이스 표면 마감 | CMP 연마 |

| 28 | C면 표면 마감 | 광학적으로 연마 |

2. SiC Epi Wafer 제조 공정에서 Epilayer 도핑 농도를 제어하는 방법은 무엇입니까?

에피택셜 층의 도핑 유형과 농도를 제어하는 것은 SiC 전력 장치의 성능에 매우 중요하며, 이는 후속 장치의 특정 온 저항 및 차단 전압과 같은 중요한 전기적 파라미터를 직접 결정합니다. 연구진이 발견한 경쟁력 있는 에피택시 방법은 N형과 P형의 도핑 농도를 광범위하게 효과적으로 변화시킬 수 있어 실제 생산에 널리 사용되고 있다. 여기서는 N형 도핑 원소와 P형 도핑 원소인 알루미늄(Al)의 원리를 간략하게 설명한다.

에피택시 웨이퍼 제조 중에 질소(N) 원자는 격자 위치를 두고 탄소(C) 원자와 경쟁합니다. 질소(N) 원자의 도핑 농도를 줄이기 위해 에피택셜 가스 소스의 탄소(C) 원자 농도를 증가시켜야 합니다. 대조적으로, 에피택셜 가스 소스에서 탄소(C) 원자의 농도를 감소시키기 위해서는 질소(N) 원자의 도핑 농도를 증가시켜야 한다. 알루미늄(Al) 원자가 격자 위치를 놓고 실리콘(Si) 원자와 경쟁하는 동안 에피택셜 가스 소스에서 실리콘(Si) 원자의 농도를 증가시켜 알루미늄(Al) 원자의 도핑 농도를 줄일 수 있습니다. 반대로 에피택셜 가스 소스의 실리콘(Si) 원자 농도를 줄여 알루미늄(Al) 원자의 도핑 농도를 높일 수 있습니다.

SiC 에피택시 공정에서 Si 소스에 일반적으로 사용되는 가스 소스는 SiCl4 또는 SiH4입니다. C 소스에 일반적으로 사용되는 가스 소스는 CCl4 또는 C3H8입니다. 우리는 C/Si 구성비를 제어하기 위해 두 가지의 유량비를 제어할 수 있으므로 서로 다른 원소의 도핑 농도를 효과적으로 제어할 수 있습니다.

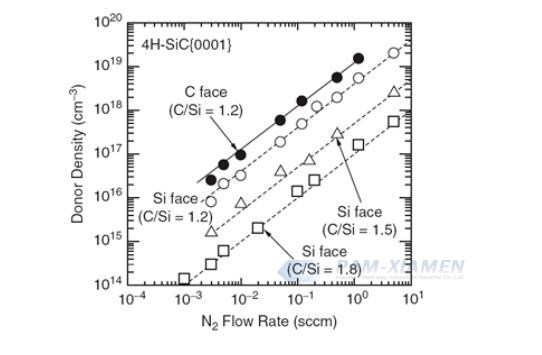

게다가, SiC 에피택셜 층의 도핑 농도는 CVD 프로세스에서 가스 소스 유량, 가스 압력 및 성장 온도와 관련이 있습니다. 추가 설명을 위해 질소(N) 도핑을 예로 들어 보겠습니다. 질소(N) 도핑은 CVD 에피택셜 성장에 질소(N2)를 도입하여 빠르게 달성할 수 있습니다. 그림 1에서 우리는 Si 및 C 표면의 도핑 농도가 고정된 C/Si 성분 비율에서 4자리 범위 내에서 N2 유량에 양의 비례함을 알 수 있습니다. SiC 에피 웨이퍼 제조 공정의 도핑 농도는 디바이스에서 가장 일반적으로 사용되는 E14-E18의 도핑 범위를 포함합니다.

그림 11550℃에서 4H-SiC 에피택시에서 질소(N) 도핑 농도와 질소(N2) 유량의 관계

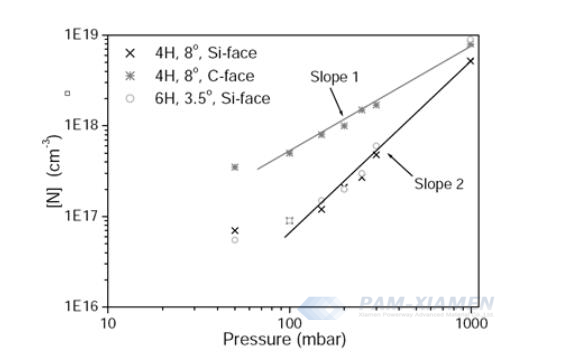

CVD 캐비티에서 SiC 에피 웨이퍼 제조 공정의 가스 압력과 도핑 농도 사이의 관계를 연구했습니다. 그림 2에서 보는 바와 같이 에피택셜 온도 1600℃, C/Si 비율 3.5, 질소 유속 12ml/min 조건에서 N원소 농도와 압력의 관계를 조사하였다. 4H-SiC의 C면 또는 Si면 에피택시가 무엇이든, 에피 반도체 웨이퍼 제조의 도핑 농도는 압력이 증가함에 따라 증가합니다.

도. (2)SiC Epi Wafer 제조 공정의 N 원소 농도와 압력의 관계

3. MOS 소자용 SiC 에피택시에 대한 FAQ

큐:귀하가 제공한 사양에 따라 4H-SiC 웨이퍼의 구조는 다음과 같습니다.

2층 4H-SiC 에피층(도핑 농도 = 1 x 10^16 cm-3)/ 1층 4H-SiC 에피층(도핑 농도 = 1 x 10^18 cm-3)/ 4H-SiC 웨이퍼(비저항 = 0.015-0.028) 옴 cm-3)

우리는 이 웨이퍼를 사용하여 MOS 캐패시터로 가공하고 정전 용량-전압 측정을 수행할 계획입니다.

일반적으로 실리콘 웨이퍼(비저항= 1-10옴)의 경우 실리콘 웨이퍼 위에 금속 산화물 층을 증착합니다. 그런 다음 상단 금속 접촉부와 하단 금속 접촉부를 증착하여 Al/금속 산화물/실리콘/금속 구조(MOS 커패시터)를 얻고 커패시턴스-전압 측정을 수행합니다.

실리콘 웨이퍼를 사용한 이전의 이해를 바탕으로 실리콘 웨이퍼의 비저항이 0.005옴(고농도로 도핑된 n형 실리콘 웨이퍼로 알려짐)인 경우 정전용량-전압 곡선을 얻을 수 없습니다.

4H-SiC 웨이퍼의 비저항은 고농도 도핑(0.015-0.028 ohmcm-3) 및 4H-SiC의 첫 번째 레이어로 간주되므로 제안된 4H-SiC 웨이퍼가 우리 연구 작업에 적합한지 귀하의 의견을 묻고 싶습니다. 에피층은 10^18 cm-3의 높은 도핑 농도를 가집니다.

실제로 4H-SiC 에피층의 두께는 우리 연구에서 그다지 중요하지 않지만 5 x 10^15 ~ 5 x 10^16 cm-3 범위의 도핑 농도가 필요합니다. 귀사에서 생산하는 맞춤형 웨이퍼와 비교할 때 더 저렴한 표준 제품이 있습니까?

:1) SiC 에피택시층의 도핑 농도는 5×10^15~5×10^16 cm-3이며, 이는 에피택셜 기술에서 달성할 수 있습니다.

2) 0.8 ~ 0.1 ohmcm-3의 비저항에 대해 비저항이 낮아 정전용량 전압 곡선을 얻을 수 없는 경우 에피택셜 농도는 낮은 도핑 농도(높은 비저항)를 고려하는 것이 좋습니다.

자세한 내용은 다음 이메일로 문의하십시오.victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.