PAM-XIAMEN은 통합 광 도파관 장치 제조를 위한 실리콘 에피택시 웨이퍼를 제공할 수 있습니다. 우리가 제공하는 실리콘 에피 웨이퍼는 Si 기판 위에 성장된 Si 코어층과 SiO2 하부 클래딩층이며 도파관 구조는 융기되어 있습니다. Si와 SiO2 물질 사이의 큰 굴절률 차이로 인해 이 구조는 빛을 최상층 실리콘 구조로 제한할 수 있고 소형 및 소형 광 도파관 장치를 쉽게 얻을 수 있습니다. 더 많은 매개변수실리콘 에피 웨이퍼, 다음과 같이 표를 보십시오.

1. 통합 도파관 광학용 Si 에피택시 웨이퍼 사양

아래의 실리콘 웨이퍼 에피택시는 통신 파장 범위의 통합 도파관 광학 장치를 제조하는 데 적합합니다.

PAM191012-SI

| 매개 변수 | 값 |

| 기판 | |

| 웨이퍼 재료 | 단결정 실리콘 |

| 웨이퍼 직경 | 100±0.2mm |

| 두께 | ≥ 500um |

| 저항 | >1옴*cm |

| 도전 형 | – |

| 정위 | – |

| 뒤틀림 | ≤50um |

| 웨이퍼 벤딩 | ≤50um |

| 예외 에지 | ≤5mm |

| 산화물층 | |

| 레이어 재료 | 산화규소 |

| 두께 | 3.0±15um |

| 대시보드 레이어 | |

| 레이어 재료 | 단결정 실리콘 |

| 두께 | 120±10nm |

| 전도도 유형 | p/B 또는 도핑 없는 자기 전도도 |

| 크리스탈 방향 | (1-0-0) ±0.5° |

| 저항 | ≥1000옴*cm |

| 표면 처리 | 세련 |

| 표면 거칠기 | ≤5A |

| 표면 오염(입자 수) | 0.3의 입자가 50개 이하 |

2. 광학 도파관 재료로 실리콘을 선택하는 이유는 무엇입니까?

광 도파관을 만들기 위해 실리콘 재료를 선택하는 이유는 주로 다음과 같습니다.

1) 실리콘의 흡수 계수 곡선은 그림 1과 같습니다. 1300 nm 이상의 파장에서 실리콘 물질의 흡수 계수는 상대적으로 작기 때문에(<1e-5/cm) 빛이 투과됨을 알 수 있습니다. 그리고 본질적인 손실은 매우 작습니다.

![]()

그림 1 실리콘의 흡수계수

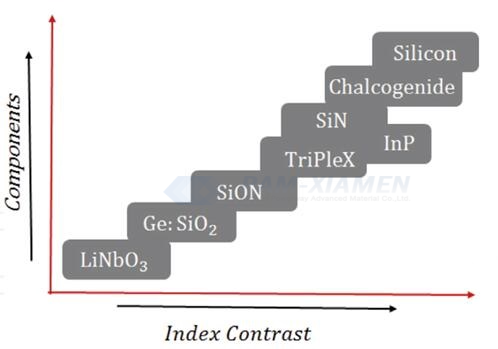

2) 실리콘의 굴절률은 3.48이고, 이산화규소의 굴절률은 1.44이며, 둘의 굴절률 대비는 0.41에 이릅니다(지수 대비 = (n1^2-n2^2)/2n1^2). 따라서 빛은 실리콘 도파관에서 더 잘 바인딩될 수 있습니다. 도파관의 크기가 작을수록 동일한 면적의 광칩에 더 많은 광소자를 포함할 수 있으며 칩 집적도가 높아집니다. 그림 2는 서로 다른 재료의 일반적인 광 도파관을 비교한 것입니다. 실리콘 에피택시 웨이퍼 기반의 도파관이 가장 높은 소자 집적도를 가지고 있음을 알 수 있습니다.

그림 2 재료에 따른 광도파로 비교

3) 도파관의 에칭, 에피택시 또는 도핑 여부에 관계없이 실리콘 에피택시 필름 웨이퍼의 처리는 비교적 간단합니다. 실리콘 도파관의 제조 공정은 대량 생산에 도움이 되는 CMOS 공정과 호환됩니다.

3. 광 도파관이란 무엇입니까?

광 도파관은 광파가 전파되도록 유도하는 매체 장치로, 매체 광 도파관으로도 알려져 있습니다. 광 도파관에는 두 가지 유형이 있습니다. 하나는 일반적으로 광전자 집적 장치(또는 시스템)의 일부인 평면(박막) 유전체 광 도파관 및 스트립형 유전체 광 도파관을 포함하는 통합 광 도파관입니다. 다른 유형은 일반적으로 광섬유라고 하는 원통형 광 도파관입니다.

여기서 평면 유전체 광 도파관은 가장 단순한 광 도파관이다. 굴절률이 n2인 실리콘(또는 갈륨 비소 또는 유리)을 기판으로 사용하고 마이크로전자 프로세스를 사용하여 굴절률이 n1인 유전체 필름과 굴절률이 n3인 클래딩 층으로 코팅합니다. . 일반적으로 n1>n2>n3을 취하여 유전막에서 전파되는 광파를 제한합니다. 스트립 모양의 유전체 광 도파관은 n1>n2를 취하여 굴절률이 n2인 매트릭스에서 굴절률이 n1인 스트립을 생성하여 스트립에서 전파되는 광파를 제한합니다. 이러한 광 도파관은 종종 광 스플리터, 커플러, 스위치 및 기타 기능 장치로 사용됩니다.

자세한 내용은 이메일로 문의하십시오.victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.