PAM-XIAMEN은 전력, E-모드용 실리콘 HEMT 웨이퍼 상의 GaN을 제공합니다. normal-on 특성은 회로 설계 및 전력 소비의 복잡성을 증가시키므로 제로 그리드 바이어스에서 꺼지는 향상된(E-모드) HEMT를 설계하는 것은 GaN-on-Silicon HEMT의 응용 프로그램을 발전시키는 데 중요합니다. 전력 분야.

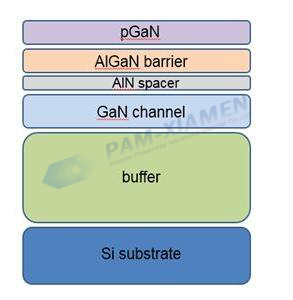

1. E-MODE의 구조의 GaN HEMT실리콘 기판에

실리콘 에피택셜 HEMT 구조의 1위 GaN

| 실리콘 HEMT 에피택시 크기의 GaN | 2 ', 4 ", 6", 8 " |

| 의 AlGaN / GaN으로 된 HEMT 구조 | 1.2을 참조하십시오 |

| 잔류 2DEG 밀도(Vg=0V) | <1e18/cm3 |

| 5x5um2의 AFM RMS(nm) | <0.25nm |

| 활 (음) | <= 30um |

| 에지 제외 | <5mm |

| p 형 질화 갈륨 | / |

| U-GaN으로 캡층 | / |

| Al 조성 | 20 ~ 30 % |

| 의 AlGaN 배리어 층 | / |

| 질화 갈륨 채널 | / |

| AlGaN으로 버퍼 | / |

| 기판 재료 | 실리콘 기판 |

| Si 웨이퍼의 두께 (μm의) | 675um(2″), 1000um(4″), 1300um(6″), 1500um(8″) |

2호 4인치 GaN/Si 에피 웨이퍼 PAM200211-HEMT

| GaN / Si HEMT 에피 구조 | ||

| 층 | 자료 | 두께 |

| 6 | p-GaN, Mg 도핑 | – |

| 5 | AlN으로 | – |

| 4 | AlGaN으로 | – |

| 3 | AlN으로 | – |

| 2 | GaN(채널층) | – |

| 1 | 버퍼(Al,Ga)N | > = 4음 |

| 기판 | Si(111), 1000+/-25um 두께, 편향 <10um | |

말:

1/ 현재, 우리의 표준 구조 AlGaN 12NM, 25% Al은 해당 매개변수 캐리어 농도 > 6e12, 이동도 > 2000, RS ~ 500, 훨씬 더 우수합니다.

2/ 현재 Mg 도핑 농도는 ~ 2e19이고 활성화 농도는 ~ 4e17입니다.

전력용 Si 에피웨이퍼의 GaN 기능:

높은 균일성과 좋은 반복성;

우수한 낮은 누설 전류;

2DEG 전송 속성;

항복 전압 ≥ 650V;

RoHS 준수

Si 기반 GaN 에피 웨이퍼의 일반적인 응용 분야:

전력 HEMT 및 저비용 CMOS 공정에 적합합니다.

전원 다이오드에 적합

2. 실리콘 HEMT의 E 모드 GaN이란 무엇입니까?

임계 전압 극성을 전환하기 위해 실리콘 HEMT 게이트의 GaN 프로세스 구조를 변경하면 향상된(E형) GaN HEMT 장치를 생성할 수 있습니다. 공정 구조 변경의 목적은 인가 전압이 없는 상태에서 게이트 아래의 2DEG를 공핍화하여 순방향 임계 전압이 2DEG에 의해 향상되어 채널을 형성할 수 있도록 하는 것입니다. P-도핑된 GaN 게이트는 게이트 구조에서 다이오드와 유사한 구조로, 다이오드 전압 강하에 의해 문턱 전압이 상승한다.

현재 p형 게이트를 사용하여 GaN 기반 강화 모드 HEMT를 구현하는 세 가지 주요 방법이 있습니다.

- p 형 게이트의 첫 번째 방법은 주로 장벽 층의 전체 에피택셜 p 형 층을 사용한 다음 게이트 아래의 p 형 층을 에칭하고 유지하여 향상을 실현하는 것입니다.

- 두 번째는 p-형 에피택셜 층을 트리밍한 다음 게이트 아래에 p-형 층을 유지하고 비게이트 영역에서 p-형 층의 대부분을 에칭하여 p-형 층의 5-20 나노미터를 남깁니다. . 에칭 과정에서 플라즈마는 인터페이스를 손상시키고 실리콘 전원 장치의 GaN 안정성에 영향을 미칩니다.

- p-형 게이트의 세 번째 방법은 p-형 게이트를 성장시키기 위해 배리어층 상의 게이트 영역에 2차 에피택시를 하는 것이다.

3. 전력용 Si 웨이퍼의 GaN, E-모드에 대한 FAQ

질문 1:Si HEMT 웨이퍼의 E-mode GaN 표면 처리에 대해: 이 어려운 문제를 극복하기 위한 힌트도 주시겠습니까? 특히 게이트 프로세스는 우리의 마음에 있습니다. 우리는 게이트 금속 증발 전의 처리에 대해 잘 모릅니다.

:Si HEMT 웨이퍼의 GaN 표면과 관련하여 pGaN 에칭 후 에칭된 표면을 수리하기 위해 유기 처리가 중요합니다.

질문 2:E-모드 HEMT를 위한 Si 에피 구조의 GaN에 대해서도 일부 시뮬레이션을 수행했으며 시뮬레이션에서 유사한 결과를 얻었습니다. 내 말은 13nm의 AlGaN 장벽이 예상되는 Vth 값에 적합하다는 것을 의미합니다. 180mA/mm를 얻을 수 있지만 이 전류 밀도는 어느 DS 거리에서 관찰됩니까?

시뮬레이션에 따르면 AlGaN 두께를 13nm로 줄이는 것은 좋지만 안전을 위해 Al 몰 분율을 0.18로 유지해야 합니다. 이것이 IDSS를 얼마나 변화시킬지 예상하십니까?

:소스에서 드레인까지의 거리는 HEMT 에피택시 구조를 기반으로 하여 ~25μm입니다. 13nm Al(0.18) GaN 장벽의 Idss에 관해서는 에칭 정확도에도 영향을 받기 때문에 말하기 어렵습니다. 참고로 우리는 12nm Al(0.15)GaN 장벽이 있는 장치에서 작업했으며 Idss는 ~72mA/mm입니다.

Q3:임계 전압이 있는 GaN-on-Si 기반 장치에 대해 다른 게이트 금속(Pd, 텅스텐, Ni, NiAu, Ti 등)을 시도했지만 항상 0.7V입니다. 최대 1.2V까지 증가시켜야 합니다. 이 문제에 대한 권장 사항도 있습니까? 당신의 지도가 많은 도움이 될 것입니다.

:항복 전압(BV) 관련: GaN/Si HEMT의 동일/유사한 epi 구조를 가진 웨이퍼는 항상 자체 팹에서 처리되며 BV > 650V(Ieakage 전류 Ids < 1μA)로 안정적인 BV 출력을 얻습니다. . 더 높은 BV는 적절한 표면 처리와 최적화된 패시베이션 층에 의해 달성되어야 합니다.

Q4:우리는 Vth를 증가시키기 위해 GaN HEMT 구조의 AlGaN 두께를 수정하는 것을 생각하고 있습니다. 어떻게 생각해? 또는 Vth를 높이기 위해 다른 것을 제안할 수도 있습니다.

:E-mode GaN/Si HEMT 웨이퍼의 임계 전압 Vth에 관하여: 우리는 Vth가 장벽 두께를 줄임으로써 향상될 수 있다고 믿습니다. 우리 팹에서 ~13nm Al0.2Ga0.8N 장벽을 사용하여 Vth > 1.5V를 가진 장치를 쉽게 얻을 수 있지만 상대적으로 높은 온 상태 전류는 여전히 유지될 수 있습니다(>180mA/mm). 귀하의 경우 AlGaN 장벽이 약간 더 두꺼워(18nm) Vth 값을 < 1V로 제한할 수 있습니다.

질문 5:Mg 도핑을 위해 어떤 종류의 활성화가 필요합니까, 아니면 Si에서 GaN의 HEMT 웨이퍼에서 도핑을 이미 활성화했습니까?

:우리는 이미 GaN-on-Si HEMT 웨이퍼에서 도핑을 활성화했습니다.

질문 6:우리는 여전히 웨이퍼에서 프로세스를 최적화하기 위해 노력하고 있습니다. 지금까지 우리는 PGaN E 모드 웨이퍼로 420V 항복을 달성할 수 있었습니다.

항복 전압에 대해 어떻게 예상하십니까? 우리는 얼마나 높이 갈 수 있습니까? 650V는 E 모드에서 약간 어려울 수 있다고 말씀하신 것이 기억납니다.

그 사이에 에피 성장에 약간의 진전이 있습니까? 고장이 650V인 D 모드 웨이퍼를 구입할 수 있습니까?

:항복 전압은 D 모드 및 E 모드 HEMT 웨이퍼 모두에서 1000V에 도달할 수 있습니다.

질문 7:수직 항복은 최대 1000V까지 올라갈 수 있으며 샘플 중 하나를 사용하여 약 900V도 측정한 것으로 기억합니다. 600v 작동의 경우 D 모드를 제안했습니다. 나는 E 모드가 그 값에 도달할 수 없다는 것을 이해합니다. 내가 틀렸어? E 모드 웨이퍼로 600V를 달성하기 위한 힌트가 있습니까?

:600v 작동에서는 이 전압에 더 적합한 D 모드 HEMT 웨이퍼를 사용하는 것이 좋습니다. 그러나 항복 전압이 언급한 대로 600v에만 도달하는 것은 아니며 둘 다 1000v에 도달할 수 있다는 의미는 아닙니다.

질문 8:현재 우리는 Si HEMT 웨이퍼의 GaN으로 장치의 항복 전압을 개선하기 위해 노력하고 있습니다. ~350V를 얻었지만 고장을 개선하기 위해 누출을 줄이는 방법을 찾고 있습니다. 그러나 그 사이에 문턱 전압에 문제가 있습니다. 더 많은 양의 전압이 필요합니다. 결과를 개선하려면 여러분의 도움과 제안이 필요합니다.

내가 염두에 두고 있는 것은 AlGaN 장벽 두께를 약간 줄이되 Al 조성을 약간만 증가시켜 N 손실을 보상하는 것입니다. 우리의 의견으로는 이것은 장치의 임계 전압을 향상시켜야 합니다. 어떻게 생각해? 이러한 매개변수를 개선하기 위해 다른 웨이퍼를 주문할 수 있습니다.

장치의 항복 전압을 개선하기 위한 제안 사항이 있습니까?

A: RE: GaN/Si 웨이퍼 상의 HEMT 장치의 항복 전압:

우리가 고객에게 전달한 웨이퍼는 수직 항복 전압이 > 1000V(@I < 1uA/mm2)인 HV 버퍼를 기반으로 합니다.

실제로 이 에피 구조에 제작된 장치에 따르면 자체 팹에서 오프 상태 누설은 Ids< 0.1uA/mm이고 Vds = 650V(Lds=15um)입니다.

에피 버퍼와 칩 공정 모두 누수의 원인이 되므로 칩 공정, 특히 누수에 중요한 역할을 하는 패시베이션층을 확인하는 것이 좋습니다.

RE: 실리콘 HEMT 웨이퍼 상의 GaN 상의 디바이스의 Vth:

더 얇은 배리어 레이어는 Vth를 확실히 높이는 데 도움이 됩니다.

AlGaN(20% Al) 두께를 12.5nm로 줄일 수 있습니다(이전 두께는 ~ 18nm).

A Vth> 2V(@Ids~10uA/mm)는 이 구조를 기반으로 우리 팹에서 입증되었습니다.

Rs를 희생하더라도 ~550ohm/sq의 Rs 값을 얻습니다.

그건 그렇고, 칩 공정, 특히 게이트 재료도 Vth에 중요합니다.

질문 9:나는 당신의 대답을 평가합니다. 고맙습니다. 우리는 또한 약 1kV를 측정하는 수직 항복 문제에 직면하지 않습니다. 그러나 DS 누설(LDS12um 사용)이 더 높고 650V를 달성할 수 없습니다.

내 관찰에 따르면 우리의 주요 문제는 게이트 누출에서 비롯됩니다. 그리고 당신이 언급했듯이 게이트 재료는 이 누출에 영향을 미칩니다. 우리는 게이트 금속으로 Ni/Au를 사용합니다. 그러나 당신의 작은 지도는 많은 가치가 있을 것입니다. 게이트 누설과 Vth를 개선하기 위한 제안은 무엇입니까? 게이트 금속 아래에 ALD 또는 이와 유사한 유전체를 사용합니까? 어떤 금속 구조를 사용합니까? 게이트 접점을 개선하기 위해 제안하는 사항은 무엇입니까?

:답장:GaN HEMT 소자 제작을 위한 게이트 금속:

당사의 생산 라인은 "Au" 프리이므로 Au가 사용되지 않으며 또한 Ni/Au 접촉은 일반적으로 높은 게이트 누출을 제공합니다.

세 가지 유형의 게이트 접촉은 Vth를 향상시킬 수 있습니다: Ni, W(wolfram) 또는 TiN(옵션).

누출에 관하여:

Vg = 0V에서 오프 상태 누설을 측정합니다.

실제로, Vth에 따라 다릅니다. Vth가 0V에 가까우면 Vg=0V에서의 누설이 높아집니다. 장치가 "꺼짐"이 완료되지 않았기 때문입니다. Vth > 1.5V인 경우 우리 장치는 Vg = 0V에서 낮은 누설(sub uA)을 제공합니다.

오프 상태 누설의 원인이 될 수 있는 에칭 불량에 주의하십시오.

위의 정보가 도움이 되기를 바랍니다.

Q10:p-GaN과 AlGaN 사이에 1 nm AlN 층을 삽입하고 싶습니다. 가능합니까?

:p-GaN과 AlGaN 사이에 1nm AlN 층을 삽입하는 데는 문제가 없지만 식각을 막는 데는 도움이 되지 않습니다.

자세한 내용은 이메일로 문의하십시오.victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.