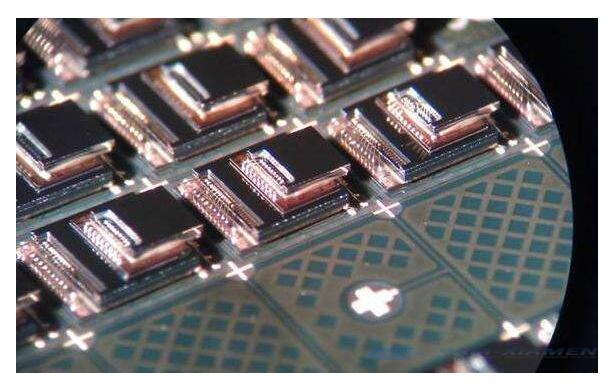

PAM-하문 MEMS 및 화합물 반도체 GaAs 마이크로웨이브 집적 회로(GaAs MMIC) 장치의 설계 및 처리에 참여하고 마이크로 나노 센서, 마이크로 전자기계 시스템(MEMS), 마이크로 나노 제조의 연구, 개발, 생산 및 서비스에 중점을 둡니다. 및 화합물 반도체 GaAs 칩. 우리는 MEMS(Micro Electro Mechanical System) 센서의 연구, 개발 및 제조를 전문으로 하는 웨이퍼 처리 서비스를 제공하는 첨단 기술 기업이며 국제 수준의 마이크로 나노 설계 및 처리 능력을 보유하고 있습니다. 다양한 MEMS 센서의 웨이퍼 생산, 패키징 및 테스트를 실현할 수 있습니다. 웨이퍼 반도체 공정으로 개발된 제품에는 비냉각 적외선 감지기, 압력 센서, 미세 유체 공학, 가스 센서 및 기타 MEMS 센서가 포함됩니다. 화합물 반도체 GaAs 집적 회로 제품에는 변형된 이종 접합 고이동도 트랜지스터(pHEMT) 전력, 저잡음 및 GaAs 광전도 스위치 및 기타 칩 처리 서비스가 포함됩니다.

또한 PAM-XIAMEN은 웨이퍼 처리 회사 중 하나로서 실리콘 웨이퍼 열 산화, 이온 주입, 포토리소그래피, RIE 에칭, PECVD와 같은 MEMS 및 GaAs와 같은 다양한 반도체 장치의 제조 및 단일 단계 및 다단계 처리 서비스를 수행합니다. , LPCVD, 마그네트론 스퍼터링, 전자빔 증착, 깊은 실리콘 에칭, 급속 어닐링, 전기 도금, 절단, 본딩, 패키징 및 기타 웨이퍼 파운드리 서비스. 모든 종류의 실리콘 웨이퍼 공급 등.

다음은 당사가 제공하는 웨이퍼 투 칩 공정 서비스입니다.

1. MEMS 2차원 재료 통합 서비스

당사의 웨이퍼 처리 기술은 MEMS에서 2차원 재료의 전송을 실현할 수 있습니다.

2. MEMS 및 반도체 Tape Out 처리 서비스

반도체 칩(예: DMOS, L-IGBT, MOSFET, PHEMT, HFET, SiC 다이오드, SiC 무선 주파수 칩 등)의 공정 개발 및 테이프 아웃 서비스 제공 가능

MEMS 칩(미세 유체/가스 센서/압력 센서 등)의 공정 개발 및 테이프 아웃 서비스도 가능합니다.

3. 폴리이미드 공정

폴리이미드(PI)는 강극성 용매에서 피로멜리트산 이무수물(PMDA)과 디아미노디페닐 에테르(DDE)를 중축합 및 필름으로 주조한 다음 이미드화하여 만듭니다. 폴리이미드는 고온 및 저온 저항, 전기 절연성, 접착력, 유전 저항, 기계적 특성 및 내방사선성이 우수합니다. -269℃-280℃의 온도 범위에서 장기간 사용할 수 있으며 단시간에 400℃의 고온에 도달할 수 있습니다. 우리는 고품질의 기술 서비스를 고객에게 제공하기 위해 PI 드라이 필름과 PI 접착제의 두 가지 유형의 장치 처리 기술을 마스터합니다.

3.1 폴리이미드 웨이퍼 처리 기술 응용

폴리이미드는 특수 엔지니어링 재료로서 항공, 항공우주, 마이크로일렉트로닉스, 나노미터, 액정, 분리막, 레이저 및 기타 분야에서 널리 사용됩니다.

3.2 PI 처리 서비스 기능

건조 필름: 두께 20-150um, 에칭 깊이 ≤15um;

감광성 솔루션: 최소 선 너비 5um, 두께 5-20um;

비감광성 용액: 에칭 깊이 0-15um.

3.3 PI 처리 서비스의 장점

우리는 건식 필름 및 PI 접착제 처리 기술을 보유하고 있으며 건식 필름 에칭 깊이는 15um에 도달 할 수 있으며 다층 PI 필름 적층 공정, 우수한 접착력을 마스터 할 수 있습니다.

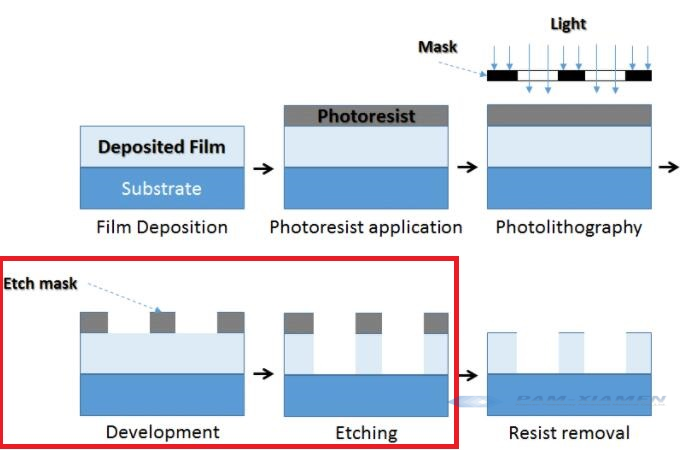

4. 웨이퍼 에칭 공정

식각은 마스크 패턴이나 설계 요구 사항에 따라 반도체 기판의 표면이나 표면 피복막을 선택적으로 식각하는 기술이다. 반도체 웨이퍼 제조 공정, 마이크로 전자 IC 제조 공정 및 마이크로 나노 제조 공정의 매우 중요한 단계 중 하나입니다. 포토리소그래피와 관련된 패턴 처리의 주요 웨이퍼 처리 솔루션 중 하나입니다. 식각 처리 서비스는 건식 식각과 습식 식각으로 구분됩니다. PAM-XIAMEN은 현재 다양한 에칭 공정을 마스터하고 있으며 고객의 요구에 따라 우수한 에칭 효과와 비용 효율적인 에칭 솔루션을 설계할 것입니다.

반도체 웨이퍼 제조 공정에서의 에칭

4.1 에칭 기술 적용

당사의 에칭 기술은 주로 반도체 장치, 집적 회로 제조, 박막 회로, 인쇄 회로 및 기타 미세 패턴의 가공에 사용됩니다.

4.2 에칭 처리 능력

에칭 기술: 이온빔 에칭, 깊은 실리콘 에칭, 반응성 이온 에칭, 집중 이온빔 및 기타 에칭 기술;

에칭 재료: 실리콘, 실리콘 산화물, 실리콘 질화물, 금속, 석영 및 기타 재료

4.3 에칭 서비스의 장점

* 다양한 에칭 기술을 마스터하십시오.

* 광범위한 에칭 재료;

* 깊은 실리콘 에칭의 최대 종횡비는 높은 에칭 정확도와 작은 선폭으로 20:1입니다.

5. 코팅 처리 서비스

진공 코팅은 진공 환경에서 기체상의 형태로 재료의 표면에 특정 금속 또는 비금속을 증착하여 조밀한 막을 형성하는 것을 말합니다. 코팅의 품질은 반도체 장치의 기능 형성에 중요합니다.

5.1 코팅 기술 적용

웨이퍼 처리 금속화는 주로 마이크로 나노 반도체 장치의 제조 공정에서 사용됩니다. 전극 제조에는 주로 금속과 ITO 물질이 사용되며 절연 유전층 및 희생 마스크층 제조에는 기타 비금속 물질이 주로 사용된다.

5.2 코팅 공정 능력

마스터 코팅 기술: 전자빔 증발 마그네트론 스퍼터링, LPCVD, PECVD, ALD, MOCVD 및 MBE.

5.3 코팅 재료

다음 재료로 코팅을 할 수 있습니다.

금속: Ti, Al, Ni, Au, Ag, Mo, Cr, Pt, Cu, Ta, TiW, Pd, Zn, W, Nb;

비금속: Si, SiO2, SiNx, TiN, Ga2O3, Al2O3, TiO2, HfO2, MgF2, ITO, Ta2O5;

압전 필름: AlN, PZT, ZnO;

코팅 기질: 실리콘 웨이퍼, 석영 유리 웨이퍼, 사파이어 웨이퍼, 탄화규소, II-IIII족 기질, III-V족 기질, PET, Pi 등

5.4 코팅 처리 서비스의 장점

* 다양한 코팅 기술과 광범위한 코팅 재료를 마스터하십시오.

* 코팅 두께 범위: 5nm-10um;

* 기본 크기는 8인치 하향 호환입니다. 코팅 균일도가 좋고 코팅이 조밀합니다.

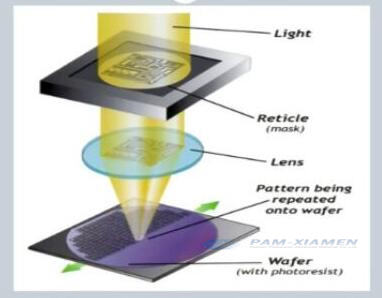

6.포토리소그래피 처리

포토리소그래피는 반도체 장치의 제조 공정에서 중요한 단계입니다. 소자 구조는 노광 및 현상에 의해 포토 레지스트 층에 묘사되고 마스크의 패턴은 식각 공정을 통해 기판에 전사됩니다. 우리는 현재 전자빔 리소그래피, 스텝 리소그래피 및 접촉 리소그래피와 같은 다양한 리소그래피 웨이퍼 공정 단계를 보유하고 있습니다.

포토리소그래피 웨이퍼 처리

6.1 리소그래피 기술 적용

리소그래피 기술은 주로 반도체 장치 및 집적 회로의 제조 공정에 사용됩니다.

6.2 포토리소그래피의 웨이퍼 처리 능력

EBL(전자빔 리소그래피): 최소 CD 값은 50nm이고 정확도는 10%에 도달할 수 있습니다.

스테퍼: 최소 CD 값은 350nm, 노출 오차는 ±0.1um, 최대 노출 영역은 6인치입니다.

접촉 및 근접 리소그래피: SUSS MA6/BA6 리소그래피 기계, 최소 CD 값 2um, 노출 오차 ±0.3um

6.3 포토리소그래피의 장점

* 고객 요구에 따라 가장 비용 효율적인 리소그래피 솔루션을 사용자 정의합니다.

* 높은 정밀도와 작은 선 너비;

* 기판 크기 범위는 1cm에서 8인치입니다.

* 높은 그래픽 충실도.

7. TSV 기술

TSV 기술은 3차원 집적 회로에 칩을 적층하여 상호 연결을 달성하기 위한 고급 웨이퍼 처리 솔루션인 Through Silicon Via Technology의 약자입니다. TSV 처리 서비스는 3차원 방향으로 칩의 적층 밀도를 최대화할 수 있고 칩 사이의 가장 짧은 배선 라인, 가장 작은 크기를 할 수 있고 칩 속도 및 저전력 소모의 성능을 크게 향상시킬 수 있기 때문에 가장 눈길을 끄는 것이 되었습니다. 현재 전자 웨이퍼 레벨 패키징 기술 중 하나입니다.

공정 수축과 저유전율 소재의 한계로 인해 3D 적층 기술은 고성능 칩을 더 작은 크기로 제조하는 능력의 핵심으로 간주되며 TSV(Through Silicon Vias)는 수직 전도를 통해 웨이퍼 적층을 통합할 수 있습니다. 칩 간의 회로 상호 연결을 달성하면 웨이퍼 프로세스 시스템의 통합 및 효율성을 더 낮은 비용으로 개선하는 데 도움이 되며 집적 회로의 3D 통합을 실현하는 중요한 방법입니다. 우리는 칩 상호 연결에 대한 요구 사항을 충족하는 완전한 TSV 프로세스를 보유하고 있습니다.

8. 부식 기술

PAM-XIAMEN은 산화물, 질화물, 실리콘, 폴리실리콘 및 게르마늄 등방성 부식, 표준 금속 부식, 비표준 절연 매체, 반도체 및 금속 부식, 포토레지스트 제거 및 실리콘 웨이퍼 세척 단계, 실리사이드 부식, 플라스틱 및 폴리머를 포함한 부식 서비스를 제공합니다. 에칭, 실리콘 이방성 에칭, 벌크 실리콘 및 실리콘 게르마늄 자체 정지 부식, 전기 화학적 부식 및 자체 정지, 광 보조 부식 및 자체 정지, 박막 자체 정지 부식, 희생층 제거, 다공성 실리콘 형성.

9. 웨이퍼 본딩 기술

본딩은 깨끗하고 원자 수준의 평평한 표면을 가진 균질 또는 이종 반도체 재료 두 조각을 표면 세정 및 활성화 처리를 거쳐 특정 조건에서 직접 접합하는 기술입니다. 웨이퍼는 반 데르 발스 힘, 분자력 또는 원자력을 통해 함께 결합됩니다. 당사는 다음과 같이 Chip to Wafer Bonding 처리 서비스를 제공합니다.

– 양극 접합(파이렉스 유리 및 실리콘 웨이퍼);

– 공융 접합(PbSn, AuSn, CuSn, AuSi 등), 솔더는 고객이 제공합니다.

– 접착제 본딩(AZ4620, SU8), 본딩 특수 접착제);

– 와이어 본딩 및 기타.

10. 패키징 기술

PAM-XIAMEN은 MPW 엔지니어링 칩의 빠른 패키징을 위한 처리 서비스를 제공합니다. 포장 유형에는 COB 빠른 밀봉, 세라믹 패키지 빠른 밀봉 및 수지 패키지 빠른 밀봉이 포함되며 다음 패키지 유형을 포함하지만 이에 국한되지 않습니다. DIP, SOP, TSSOP, SOT, TO, QFN, DFN, LGA, COB, BGA, QFP, LCC , 등.

AuSn 용접 및 세라믹 쉘의 평행 심 용접과 같은 기밀 포장 처리 서비스를 수행할 수 있습니다. 칩 그라인딩, 폴리싱, 기계적 블레이드 커팅, 실리콘 웨이퍼 레이저 논마킹 커팅, 골드 와이어 본딩, 레이저 용접, 칩 마운팅, 디스펜싱 코팅, 리플로 솔더링, 플립 칩 솔더링, 평행 밀봉 솔더링, BGA 볼 주입, 인장 전단 전단력 검사, 주사형 전자현미경 SEM 검사, X-Ray 검사, 초음파 주사 비파괴 검사 및 표면 거칠기 검사 등

11. 감지 기술

TEM, SEM, XRD, AFM, XPS, XRD, 초음파현미경, X-ray, step meter, profiler, film thickness meter, Raman 등 다양한 검출기술을 보유하고 있습니다.

자세한 내용은 다음 주소로 이메일을 보내주십시오. victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.