Kebanyakan peranti elektronik SiC tidak direka secara langsung dalam wafer tumbuh pemejalwapan, tetapi sebaliknya direka dalam lapisan SiC epitaxial kualiti yang lebih tinggi yang ditanam di atas wafer tumbuh pemejalwapan awal. Epilayer SiC yang tumbuh dengan baik mempunyai sifat elektrik yang unggul dan lebih terkawal dan boleh dihasilkan semula daripada bahan wafer SiC yang ditanam dengan pemejalwapan pukal. Oleh itu, pertumbuhan terkawal epilayer berkualiti tinggi adalah sangat penting dalam merealisasikan elektronik SiC yang berguna. Sebagai salah satu pengeluar wafer epitaxial terkemuka, PAM-XIAMEN boleh melakukanEpitaksi SiCpada substrat SiC. Spesifikasi terperinci sila ambil wafer SiC dengan filem epitaxial di bawah sebagai contoh:

1. Specification of SiC Epi Layer Structure PAMP16192-SIC

2″ diameter SiC

4H

Semi-penebat

Mati 4 darjah

Ketebalan 300-500um

Si-muka

Sebelah dua digilap, dan orientasi untuk separa penebat ialah C (0001)

Filem epitaxial:

1um tebal

Tiada doping yang disengajakan

Tandakan:

Muka Si atau muka karbon tidak relatif dengan separa penebat, biasanya muka Si digilap, sedia epi. Atau kita katakan orientasi C (0001). Juga untuk separa penebat, C (0001) adalah untuk arus perdana, dan semua pengeluar substrat melakukan pada paksi, bukan 4 darjah dimatikan;

Penyingkiran 4 darjah diperlukan untuk melaksanakan epitaksi SiC berkualiti baik pada wafer SiC.

2. Paramerter untuk Epilayers 4H-SiC

Kepekatan elektron terendah yang pernah diterbitkan ialah sekitar 1E14cm3. Ia biasanya memerlukan parameter pertumbuhan khas yang menghasilkan lebih banyak kecacatan permukaan dalam lapisan.

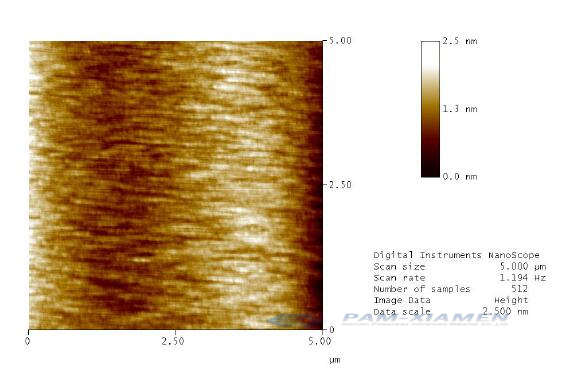

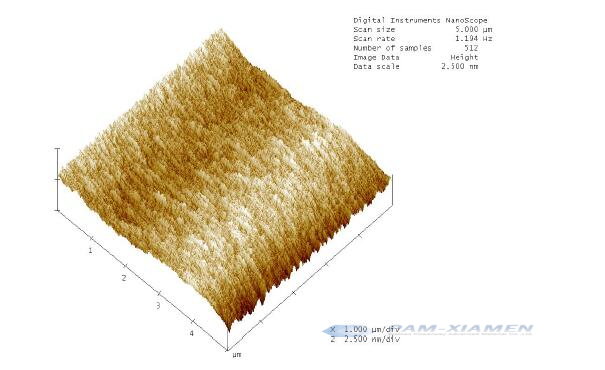

Kami mengukur CV (kepekatan pembawa) dan mengira rintangan dengan cara yang paling popular. Untukdilampirkan AFMfilem epi SiC yang tidak didop, kepekatannya ialah 1E15cm3.

3. Dopan dalam Substrat SiC dan Epilayer

Untuk spesifikasi lapisan epitaxial SiC pada substrat SiC separa penebat yang dibincangkan di atas, satu kebimbangan besar daripada pelanggan ialah penggabungan nitrogen, vanadium atau dopan lain yang tidak disengajakan akan menjadikan lapisan epi wafer, lapisan penampan jenis-n semasa pertumbuhan epitaxial.

Sebenarnya, tidak ada keperluan untuk lapisan penampan kerana substrat adalah separa penebat, dan ini adalah homo-epitaxy (SiC pada SiC). Substrat tidak didop lebih baik tetapi dalam kes vanadium ia masih berfungsi. Pekali resapan dalam SiC adalah sangat rendah. Selain itu, Nitrogen sebagai bendasing sentiasa ada dalam epi SiC yang tidak didop dan lapisannya sentiasa jenis-n. Perkaranya ialah berapa banyak doped. Dan kami boleh menjamin bahawa ia akan serendah mungkin tanpa merendahkan permukaan/kristal.

4. Pencirian untuk Permukaan Wafer SiC Epi

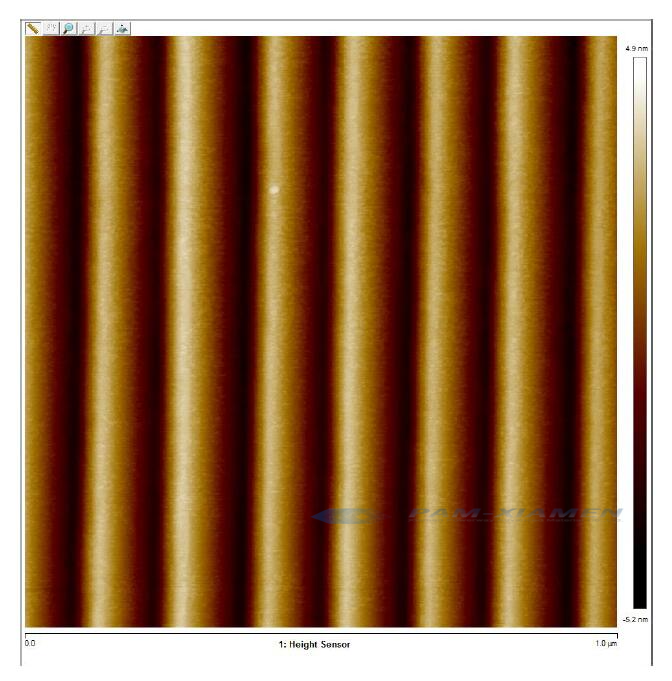

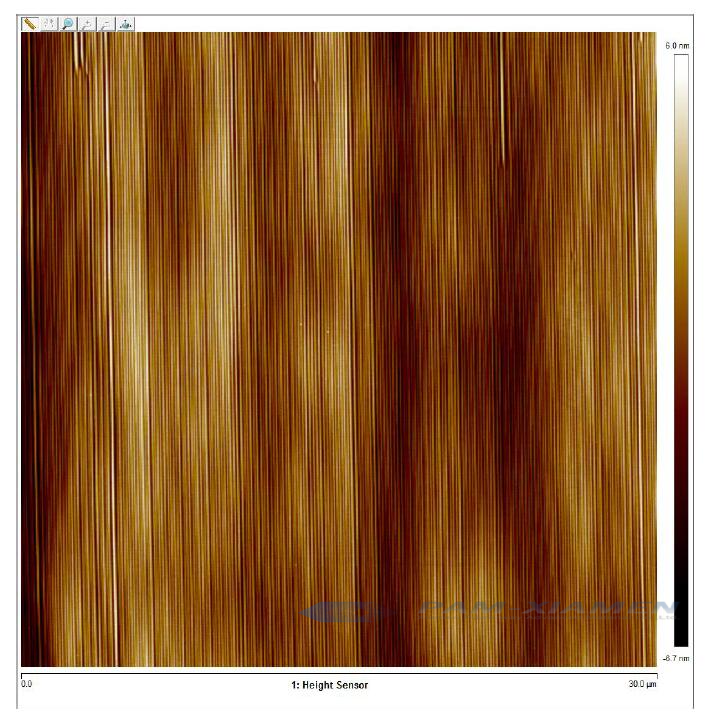

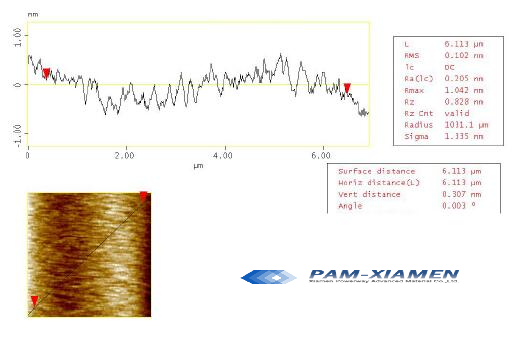

Diperhatikan melalui imej AFM di atas, permukaan dengan rabung kelihatan sangat kasar, yang disebabkan oleh langkah tandan. Pencantuman langkah sentiasa ada tetapi kita boleh mengawal ketinggian langkah dalam beberapa julat. Itu adalah contoh di mana kami ingin mendapatkan kualiti struktur lapisan yang baik. Kekasaran substrat SiC akan sentiasa lebih rendah selepas menggilap tetapi kualiti struktur (kristalografi) permukaan sedemikian adalah sangat lemah. Jika anda ingin menghasilkan peranti yang baik, kesan tandan langkah adalah "perlu" dan ia tidak mempengaruhi prestasi peranti. Sebagai contoh, kami menggunakan kekasaran 10nm untuk pertumbuhan graphene. Dilampirkan satu lagi keputusan AFM untuk rujukan anda:

Untuk tujuan tertentu, epilayer yang licin adalah lebih penting. Kekasaran lapisan epi SiC mengandungi dua parameter: langkah mikro dan langkah makro yang disambungkan ke tandan langkah. Kami akan mengawal dua parameter dalam proses pembuatan wafer epi untuk mendapatkan permukaan epilayer yang lebih licin dan memenuhi keperluan anda.

Untuk maklumat lebih lanjut, sila hubungi kami melalui e-mel di victorchan@powerwaywafer.com dan powerwaymaterial@gmail.com.