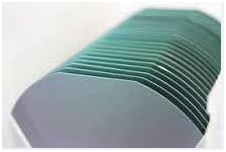

A epitaxia de silício com dopante de boro no tamanho 200 mm da PAM-XIAMEN está disponível para a fabricação de dispositivos semicondutores. O crescimento de epitaxi de silício é um processo de tratamento de superfície para wafers de silício, o que significa que um único filme de cristal é sobreposto ao wafer polido por reação química ou outro meio, e a camada de filme é a camada epitaxial de silício. Para saber mais detalhes sobre a epitaxia à base de silício de 200 mm, consulte a tabela listada.

1. Parâmetros da bolacha epitaxial de silício

PAM210531-SIEPI

| 200mm Epitaxial Silicon Wafer | |||||

| ltem | Unidades | limites | Método de teste | Comentários | |

| 1 Cristal / Características em Massa | |||||

| 1.1 | Método crescimento | – | – | – | CZ |

| 1.2 | Orientação | – | (100) | – | – |

| 1.3 | dopante | – | Boro | – | – |

| 1.4 | Resistividade | Ohm * cm | 0.01-0.02 | – | – |

| 1.5 | Variação da resistividade radial | % | 10% máx. | ASTM F81 plano B | |

| 1.6 | Concentração de oxigênio | ppma | 10-16 | Novo ASTM (F121-83) K = 2,45 | |

| 1.7 | Variação de oxigênio radial | % | ≤10% | – | – |

| 1.8 | Concentração de metais a granel, Fe | At / cm3 | NA | – | Cu / Fe / Ni / Al / Zn |

| 1.9 | Concentração de carbono | At / cm3 | Max 2.0 * 1016 | – | – |

| 1.10 | Deslocamentos | – | Nenhum | – | Após Gravura |

| 1.11 | Escorregar, Linhagem, Gêmeo, Redemoinho, Poços Rasos | – | – | ||

| 2 Wafer / Substrato Polido | |||||

| 2.1 | Orientação superfície | Grau | (100) ± 0,5 | – | – |

| 2.2 | Diâmetro | milímetros | 200 ± 0,2 | – | – |

| 2.3 | Espessura | milímetros | 725 ± 20 | – | – |

| 2.4 | Comprimento Plano primária | milímetros | Entalhado | – | SEMI M1.9-0699 |

| 2.5 | Orientação plana primária | Grau | {100} | – | – |

| 2.6 | Edge Profi (ângulo) | – | SEMI | – | – |

| 2.7 | Características de inspeção visual da superfície frontal especificadas de acordo com SEMI M1-0200 Tabela 1 | ||||

| 2.8 | Superfície do verso

Poly + LTO (SiO2) |

Poli

8000 ± 800 + LTO8000 ± 800A LTO externo |

– | – | |

| 2.9 | Exclusão de borda (LTO)

- verso - lado frontal |

milímetros | 0,5 ~ 2,0

Nenhum |

– | – |

| 2.10 | Características de inspeção visual da superfície posterior especificadas de acordo com SEMI M1-0200 Tabela 1 | ||||

| 3 Wafer / Camada Epitaxial | |||||

| 3.1 | Metais de superfície | At / cm-2 | ≤5E10 | – | Cu / Fe / Ni / Al / Zn |

| 3.2 | Arco / Urdidura | μm | ≤50 | – | – |

| 3.3 | Variação de espessura total (TTV) | μm | ≤4 | – | – |

| 3.4 | Nivelamento do local (SFQR) | μm | ≤1 | – | 20 * 20 mm, 100%

PUA |

| 3.5 | dopante | – | Boro | – | – |

| 3.6 | Faixa de Alvo de Espessura | milímetros | De acordo com o código epi para anexo | ||

| 3.7 | Tolerância de espessura, w / w | % | <5 | Centro (1 pt) 10 mm da borda (4 pontos a 90 graus)

[Tmax-Tmin] ÷ [Tmax + Tmin] * 100% |

|

| 3.8 | Faixa de resistividade | Ohm * cm | De acordo com o código epi para anexo | ||

| 3.9 | Tolerância de resistividade, w / w | % | <5 | Centro (1 pt) 10 mm da borda (4 pontos a 90 graus)

[Rmax-Rmin] ÷ [Rmax + Rmin] * 100% |

|

| 3.10 | Edge Crown | – | NA | A projeção acima da superfície do wafer não deve exceder 1/3 da espessura da camada epi | |

| 3.11 | Falhas de empilhamento | cm-2 | ≤0.1 | ASTM F1810 | – |

| 3.12 | Etch Pit Densidade | cm-2 | ≤5 | – | – |

| 3.13 | Linha Deslizante | – | SEMI M2-0997 | ASTM F523, SEMI M17 | – |

| 3.14 | Arranhões, covinhas, cascas de laranja,

Rachaduras / fraturas, pés de galinha, neblina, Assuntos do estrangeiro |

– | Nenhum | ASTMF523 | – |

| 3.15 | Edge Chips | – | Nenhum | ASTMF523 | |

| 3.16 | Defeito de ponto de luz (protrusão, intrusão,

Spike, etc) |

EA

μm |

Nenhum | ASTMF523 | Inspeção automática de superfície a laser |

| 3.17 | Exclusão de borda nominal | milímetros | 3 | Para os itens 3.2 ~ 3.4, 3.11 ~ 3.14, 3.16 | |

| Características de inspeção visual da superfície frontal especificadas de acordo com SEMI Tabela 5 SEMI M11-0200 | |||||

| 4.1 | Lazer marcação na superfície traseira dura, oposta ao entalhe, SEMI M12 | ||||

| Características de inspeção visual da superfície posterior especificadas de acordo com SEMI Tabela 5 SEMI M11-0200 | |||||

Attachment for Technical Specification Epi

| Faixa de resistividade Ohm * cm | Faixa de espessura mm | ||

| 1 | MM6Bp 12.0_15.0 | 12 ± 10% | 15 ± 5% |

2. Processo Epitaxial de Silício

A tecnologia para epitaxia em silício foi desenvolvida na década de 1960 e se desenvolveu principalmente em três métodos: epitaxia de fase gasosa, epitaxia de fase líquida e epitaxia de feixe molecular de wafer de silício. Dentre elas, a epitaxia de fase líquida e a epitaxia de feixe molecular são basicamente utilizadas apenas em laboratórios devido ao alto custo. A tecnologia de epitaxia de silício mais importante do mundo é a epitaxia de fase de vapor.

O princípio da epitaxi em fase de vapor é usar alguns gases intermediários, como tetracloreto de silício (SiCl4), tetrahidrogênio de silício (SiH4), triclorossilano de silício (SiHCL3), etc., para gerar átomos de silício nos reatores de crescimento epitaxial de silício e depositar o silício átomos em um substrato de silício monocristalino.

Tome como exemplo a reação de redução do hidrogênio com tetracloreto de silício. O gás tetracloreto de silício reage com o hidrogênio a uma temperatura elevada de 1200 ° C (a equação química é: SiCl4 + 2H2 = Si + 4HCl) para gerar um átomo de silício sólido de Si e o gás HCl como subproduto da reação. Ao mesmo tempo, os átomos de silício se acomodam no substrato para formar uma camada epitaxial.

3. Melhor desempenho da produção de wafer de silício epitaxial

A tecnologia epitaxial foi inventada pela primeira vez para resolver a contradição entre dispositivos de alta frequência e alta potência, não apenas reduzindo a resistência, mas também exigindo materiais para suportar altas tensões e altas correntes (alta resistência). Por meio da epitaxia, uma alta resistênciacamada epitaxial de wafer de silíciopode ser cultivado em um substrato de baixa resistência, de modo que os dispositivos fabricados nas estruturas epitaxiais de silício possam obter simultaneamente alta voltagem do coletor e baixa resistência do coletor.

4. Vantagens do silício epitaxia

Além do propósito do design original, a tecnologia epitaxial também tem o seguintevantagens:

4.1 Superfície de silicone epitaxi perfeita

A camada epitaxial pode melhorar a pureza e uniformidade do material na epitaxia de silíciosuperfície. Comparado com wafers mecanicamente polidos, os wafers de silício processados epitaxialmentetêm maior planicidade de superfície, maior limpeza, menos micro defeitos e menos impurezas de superfície, de modo que a resistividade é mais uniforme. É mais fácil controlar as partículas de superfície, falhas de empilhamento, deslocamentos, defeitos das camadas epitaxiais de silício, etc. A epitaxia de silício não apenas melhora o desempenho do detector de silício epitaxial, mas também garante a estabilidade e confiabilidade do produto.

4.2 Estratificação de estrutura

O epitaxial pode sobrepor uma camada epitaxial com diferentes resistividade, elementos de dopagem e concentração de dopagem de epitaxilo de silício no substrato original, que é o processo necessário para a fabricação do transistor semicondutor HBT (transistor bipolar heterojunção), MOSFET (Transistor de efeito de campo semicondutor de óxido metálico). Ao mesmo tempo, uma vez que a epitaxia fornece diferentes camadas estruturais (diferentes resistências em diferentes camadas), a epitaxia também é um dos métodos mais comuns para resolver o efeito de engate mais comum e o efeito de canal curto da tecnologia CMOS.

4.3 Retrodopagem

Dopagem se refere ao processo de introdução deliberada de impurezas em materiais puros e livres de impurezas (semicondutores intrínsecos) no processo de fabricação de semicondutores para alterar as propriedades elétricas dos materiais. A dopagem pode ser dividida em dopagem pesada, dopagem leve e dopagem média de acordo com a quantidade de elementos dopados. Em circunstâncias normais, o doping pesado deve estar acima do doping leve. Por meio do processo de silício epitaxial, a troca de camadas estruturais dopadas ou a combinação de dopagens múltiplas pode ser realizada, o que melhora a flexibilidade e o desempenho do projeto do dispositivo em epitaxia de silício.

Para obter mais informações, entre em contato conosco pelo e-mail victorchan@powerwaywafer.com e powerwaymaterial@gmail.com.