You can buy silicon epi wafer from PAM-XIAMEN, an epitaxial wafer supplier you want to find, which can offer silicon epi wafer or custom silicon epi wafer. The size we can offer is 2”, 4”, 5”, 6” or 8”. More details please see the wafer list of Si epi wafers as following:

![]()

1. Wafer List of Silicon Epitaxial Wafer

| Wafer No. | Size | Type | Thickness(um) | Resis(Ohm.cm) | EPI (Type) | EPI Thickness(μm) | EPI Resis(Ohm.cm) | Quantity(pcs) |

| PAM-XIAMEN-WAFER-#E3 | 4″ | P111 | 500±15 | — | P111 | 14.5-16.5um | 6.5-7.5 | 34 |

| PAM-XIAMEN-WAFER-#E4 | 4″ | P111 | 500±15 | — | P111 | 11-13um | 3-3.6 | 33 |

| PAM-XIAMEN-WAFER-#E5 | 4″ | P111 | 500±15 | — | P111 | 15±1.5um | 2.5±0.25 | 19 |

| PAM-XIAMEN-WAFER-#E6 | 4″ | P111 | 500±15 | — | P111 | 15±1um | 5.5±0.5 | 20 |

| PAM-XIAMEN-WAFER-#E7 | 2″ | GaAs Epi Wafer | 350um | Voltage 1-10,Luminance 100-115 | Wavelength 600-607 | 1.8-2.2 | — | 8 |

| PAM-XIAMEN-WAFER-#E8 | 2″ | GaN Epi Wafer | 430um Sapphire Substrate | — | — | Epi layer 4.7-9.1um | — | 2 |

| PAM-XIAMEN-WAFER-#E9 | 6″ | P100 | 400±10 | 8-12 | N100 | 20±10% | 3.0-5.0 | 50 |

| PAM-XIAMEN-WAFER-#E10 | 5″ | P100 | 525±15 | — | P100 | 21 | <24 | 10 |

| PAM-XIAMEN-WAFER-#E11 | 5″ | N100 | 625±15 | 0.001-0.005 | N100 | 8.5±0.51 | 0.9±0.05 | 13 |

| PAM-XIAMEN-WAFER-#E12 | 5″ | P100 | 525±15 | 0.005-0.020 | P100 | 36-44 | 30-44 | 15 |

| PAM-XIAMEN-WAFER-#E13 | 5″ | N100 | 525±15 | — | N100 | 21 | 60 | 5 |

2. What is Silicon Epitaxial Wafer?

Silicon epi wafers were first developed around 1966, and achieved commercial acceptance by the early 1980s.[5] Methods for growing the epitaxial layer on monocrystalline silicon or other wafers include: various types of chemical vapor deposition (CVD) classified as Atmospheric pressure CVD (APCVD) or metal organic chemical vapor deposition (MOCVD), as well as molecular beam epitaxy (MBE). Two “kerfless” methods (without abrasive sawing) for separating the epitaxial layer from the substrate are called “implant-cleave” and “stress liftoff”. A method applicable when the epi-layer and substrate are the same material employs ion implantation to deposit a thin layer of crystal impurity atoms and resulting mechanical stress at the precise depth of the intended epi layer thickness. The induced localized stress provide a controlled path for crack propagation in the following cleavage step.[7] In the dry stress lift-off process applicable when the epi-layer and substrate are suitably different materials, a controlled crack is driven by a temperature change at the epi/wafer interface purely by the thermal stresses due to the mismatch in thermal expansion between the epi layer and substrate, without the necessity for any external mechanical force or tool to aid crack propagation. It was reported that this process yields single atomic plane cleavage, reducing the need for post lift-off polishing, and allowing multiple reuses of the substrate up to 10 times.

3. Standard Method for Testing Thickness and Total Thickness Variation of Silicon Epi Wafer

There are two main methods for testing the thickness and total thickness variation of silicon epitaxy in the industry, including discrete point measurement and scanning measurement.

3.1 Testing Thickness of Si Epi Wafer by Discrete Point Measurement

The thickness of the silicon epitaxial wafer was measured at the center point of the silicon wafer and at 4 symmetrical points on the circumference of 6mm from the edge of the silicon wafer. Two of the points are located on a diameter of 30° in the counterclockwise direction of the bisector perpendicular to the main reference plane of the silicon epiwafer, and the other two points are located on another diameter perpendicular to the diameter (see Figure 1). The center point of the epi silicon wafer. The thickness is regarded as the nominal thickness of the epitaxial silicon wafer. The difference between the maximum thickness and the minimum thickness among the five thickness measurements is called the total thickness variation of the silicon wafer.

Fig. 1 Measuring Point Location

3.2 Scanning for Measuring the TTV of Silicon Epi Wafer

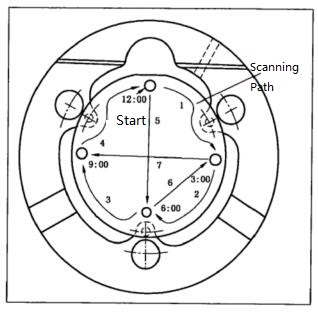

The silicon wafer is supported by three hemispherical tops on the reference ring, and the thickness is measured at the center point of the silicon epi wafer. The measured value is the nominal thickness of the Si wafer. Then scan the surface of the Si epitaxy according to the prescribed pattern to measure the thickness, and the automatic indicator shows the total thickness variation. The scanning path diagram is shown in Figure 2.

Fig. 2 Scanning Path

3.3 Interferences for Measuring Si Epi Wafer TTV

For discrete point measurement, the total thickness variation of the discrete point measurement is only based on the measurement data of 5 points, the irregular geometric changes of other parts on the silicon wafer epitaxial layer cannot be detected. A local change of a certain point on the silicon wafer may produce erroneous readings. This local change may originate from surface defects such as chipping, contamination, hillocks, pits, knife marks, ripples, etc.

As for the scanning measurement, during the scanning, any change in the reference plane will cause an error in the measurement indication value, which is equivalent to the deviation of the axis vector value of the difference between the maximum and minimum values on the probe axis. If this change occurs, it may result in the calculation of extreme values at incorrect locations. The non-parallelism of the reference plane and the granite datum plane will also cause the error of the test value. In addition, foreign particles and contamination between the reference ring and the granite platform will cause errors.

For more information, please contact us email at victorchan@powerwaywafer.com and powerwaymaterial@gmail.com.