Do ưu điểm của độ dẫn nhiệt cao, cường độ trường đánh thủng cao, tốc độ trôi điện tử bão hòa cao và năng lượng liên kết cao, vật liệu SiC có thể đáp ứng các yêu cầu mới của công nghệ điện tử hiện đại về nhiệt độ cao, tần số cao, công suất cao, điện áp cao và khả năng chống bức xạ , vì vậy nó được coi là một trong những vật liệu hứa hẹn nhất trong lĩnh vực vật liệu bán dẫn.PAM-Hạ Môncó thể cung cấp wafer tinh thể hạt 4H-SiC, được áp dụng cho sự phát triển tinh thể SiC 4 hoặc 6 inch. Vui lòng tham khảo các bảng sau để biết các thông số cụ thể.

1. Thông số kỹ thuật của SiC Seed Wafer

Ứng dụng SiC Seed Wafer: phát triển các tinh thể đơn SiC trong 4 hoặc 6 inch

1.1 Bánh tinh thể hạt 4H-SiC dày 800um

|

Thông số Wafer Seed 4H-SiC |

||||

| Không. | ltems | Sản lượng | Nghiên cứu | Đơn vị |

| 1 | Thông số pha lê | |||

| 1.1 | POLYTYPE | 4H | 4H | |

| 2 | Thông số cơ học | |||

| 2.1 | Đường kính | 104/150/13 ± 0,5mm | 104/150/13 ± 0,5mm | mm |

| 2.2 | Độ dày | 800 ± 50um | 800 ± 50um | um |

| 2.3 | bằng phẳng | Không ai | Không ai | um |

| 2.4 | TTV | ≤10um | ≤20um | um |

| 2.5 | LTV | ≤5um (5mm * 5mm) | ≤10um (5mm * 5mm) | um |

| 2.6 | Cây cung | -35um-35um | -45um ~ 45um | um |

| 2.7 | Làm cong | ≤40um | ≤50um | um |

| 2.8 | Mặt trước (Si-face) Độ nhám | Ra≤0,2nm (5um * 5um) | Ra≤0,2nm (5um * 5um) | nm |

| 3 | Kết cấu | |||

| 3.1 | Micropipe Mật độ | ≤1ea / cm2 | ≤5ea / cm2 | ea / cm2 |

| 3.2 | Khoảng trống hình lục giác | Không ai | Không ai | |

| 3.3 | BPD | ≤2000 | NA | ea / cm2 |

| 3.4 | TSD | ≤500 | NA | ea / cm2 |

| 4 | Chất lượng mặt trước | |||

| 4.1 | Trước mặt | Si | Si | |

| 4.2 | Hoàn thiện bề mặt | Si-face CMP | Si-face CMP | |

| 4.3 | vết trầy xước | ≤5 cái , ≤2 * Đường kính (Độ dài tích lũy) |

NA | ea / mm |

| 4.4 | Vỏ cam / vết bẩn / vết nứt / ô nhiễm | Không ai | Không ai | mm |

| 4.5 | Mép cạnh / vết lõm / đứt gãy / tấm lục giác | Không ai | Không ai | |

| 4.6 | Khu vực đa dạng | Không ai | ≤30% (Diện tích tích lũy) | |

| 4.7 | Đánh dấu laser phía trước | Không ai | Không ai | |

| 5 | Chất lượng trở lại | |||

| 5.1 | Kết thúc trở lại | C-face CMP | C-face CMP | |

| 5.2 | vết trầy xước | ≤2pcs , ≤Diameter (Độ dài tích lũy) |

NA | ea / mm |

| 5.3 | Khuyết tật mặt sau (chip cạnh / vết lõm) | Không ai | Không ai | |

| 5.4 | Độ nhám trở lại | Ra≤0,2nm (5um * 5um) | Ra≤0,2nm (5um * 5um) | nm |

| 5.5 | Đánh dấu bằng laser trở lại | 1mm (từ cạnh trên) | 1mm (từ cạnh trên) | |

| 6 | Bờ rìa | |||

| 6.1 | Bờ rìa | Gọt cạnh xiên | Gọt cạnh xiên | |

| 7 | Bao bì | |||

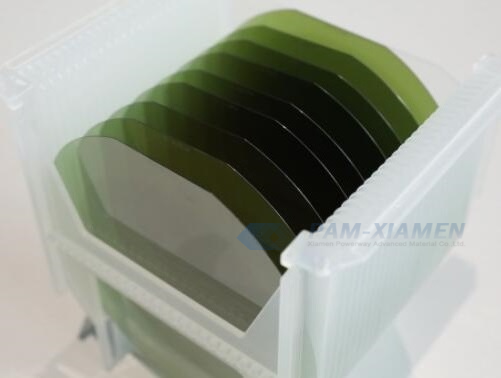

| 7.1 | Bao bì | Băng cassette nhiều tấm | Băng cassette nhiều tấm | |

1,2 4H-SiC Seed Wafer dày 430 ~ 570um

|

Thông số kim loại hạt 6 inch SI 4H-SiC |

||

| Không. | Mục | Tham số |

| 1 | Thông số pha lê | |

| 1.1 | POLYTYPE | 4H |

| 2 | Thông số cơ học | |

| 2.1 | Đường kính | 150 + 0,1mm / -0,3mm |

| 2.2 | Độ dày | 430um ~ 570um |

| 2.3 | Surface Định hướng | 1 + 0,4 ° / 2 ± 0,5 ° |

| 2.4 | Định hướng phẳng chính | {10-10} ± 0,5 ° |

| 2.5 | chiều dài phẳng chính | 0-25mm hoặc khía |

| 2.6 | Căn hộ thứ cấp | không ai |

| 2.7 | Điện trở | NA |

| 3 | Chất lượng Wafer | |

| 3.1 | Mật độ vi chạm * | <1 cm-2 |

| 3.2 | Khu vực dày đặc Micropipe * | ≤3 địa điểm |

| 3.3 | Vết xước phía trước | không ai |

| 3.4 | Khoai tây chiên* | NA |

| 3.5 | Vết nứt * | NA |

| 3.6 | Hố * | không ai |

| 3.7 | Vỏ cam* | không ai |

| 3.8 | Ô nhiễm | không ai |

| 3.9 | Khu vực đa dạng * | 0% (khu vực loại bỏ cạnh 180 ° đối diện với mặt phẳng thứ cấp) |

| 3.10 | Đa tinh thể * | không ai |

| 4 | Laser Marking | |

| 4.1 | Laser Marking | Phía trên mặt phẳng chính trên mặt Si |

| 5 | Bờ rìa | |

| 5.1 | Khu vực loại bỏ cạnh | 3mm |

| Lưu ý:”*” dữ liệu không chứa các vùng loại bỏ cạnh | ||

1.3 Tinh thể hạt 4Inch của SiC

|

Tinh thể hạt giống SiC 4Inch |

||

| Cấp | Sản lượng | Nghiên cứu |

| Đường kính | 100/105±0,5mm | |

| Độ dày | 400±100um | 400±150um |

| Định hướng | 4±1°(0±1°) | |

| Hướng phẳng chính | {1010}±0,5° | |

| chiều dài phẳng chính | 32,5mm±2,0mm | |

| Chiều dài phẳng thứ cấp | 18,0mm±2,0mm | |

| Khu vực loại bỏ cạnh | 2mm | 3mm |

| TTV | ≤10um | 15um |

| độ nhám bề mặt | C: Ra<1nm Si: Ra<1nm |

|

| Khu vực đa dạng * | Không ai | |

| Đa tinh thể * | Không ai | |

| Khoảng trống lục giác* | Không ai | |

| Mật độ micropipe* | 1cm-2 | 5cm-2 |

| Bao gồm | 1% | ≤5% |

| Các vết nứt | Không ai | cạnh<10mm, trung tâm<5mm |

| Khoai tây chiên | Không ai | - |

| Vết xước vĩ mô | Không ai | - |

| vỏ cam | Không ai | - |

| hố | Không ai | - |

| Ô nhiễm bề mặt | Không ai | Không ai |

| Ghi chú :Các khuyết tật “*” trong khu vực loại bỏ cạnh được loại trừ. | ||

2. Tinh thể hạt là gì?

Tinh thể hạt là một tinh thể nhỏ có hướng tinh thể giống với tinh thể mong muốn và là hạt giống để phát triển một tinh thể đơn lẻ. Sử dụng các tinh thể hạt có hướng tinh thể khác nhau làm hạt, sẽ thu được các đơn tinh thể có hướng tinh thể khác nhau. Theo công dụng, có tinh thể hạt đơn tinh thể Czochralski, tinh thể hạt nóng chảy vùng, tinh thể hạt sapphire và tinh thể hạt SiC.

Trong đó, SiC wafer được sử dụng như một loại tinh thể hạt cho sự phát triển của tinh thể SiC, và hình dạng của SiC seed wafer chủ yếu ở dạng màng mỏng. Có thông tin cho rằng ứng dụng của tinh thể hạt đóng một vai trò quan trọng trong sự phát triển của tinh thể SiC. Dạng tinh thể và đặc tính bề mặt của hạt SiC ảnh hưởng rất nhiều đến kiểu phát triển, cấu trúc khuyết tật và tính chất điện của tinh thể SiC.

Trong số đó, yếu tố quan trọng nhất quyết định kiểu đa tinh thể là định hướng tinh thể của tấm hạt SiC. Thỏi 6H-SiC được nuôi cấy trên bề mặt SiC (0001, Si) bằng phương pháp PVT, mặc dù tấm hạt giống là 4H-SiC (0001). Ngược lại, thỏi 4H-SiC được nuôi cấy trên mặt SiC (0001, C) bằng phương pháp PVT, không liên quan gì đến polytype của tinh thể hạt.

3. Làm thế nào để tạo ra một tinh thể hạt giống?

Để sản xuất tinh thể hạt, trước hết cắt một lượng lớn tinh thể SiC thành các màng mỏng, sau đó mài, đánh bóng và khắc màng mỏng để loại bỏ các vết rỗ và vết xước do cắt. Mài loại bỏ lớp rỗ trên bề mặt tấm wafer, để lại những vết xước mỏng, thưa thớt trên bề mặt tấm wafer. Đánh bóng có thể loại bỏ các vết xước tạo ra trong quá trình mài, nhưng không loại bỏ hoàn toàn lớp suy giảm mài hoặc lớp hư hỏng cơ học mỏng do đánh bóng tạo ra. Khắc không chỉ có thể làm lộ các khuyết tật cấu trúc trong tấm wafer, mà còn loại bỏ lớp hư hỏng cơ học bề mặt được tạo ra trong quá trình mài và đánh bóng. Wafer khắc được sử dụng như một wafer hạt, và tinh thể tăng trưởng có thể tái tạo tốt cấu trúc của tinh thể hạt, và bề mặt tinh thể nhẵn.

4. Tại sao Sử dụng SiC Seed Substrate để Phát triển Đơn Tinh thể?

Hầu hết các đơn tinh thể bán dẫn có thể được nuôi cấy từ trạng thái nóng chảy hoặc dung dịch, nhưng bản thân các đặc tính của SiC khiến không thể nuôi cấy đơn tinh thể bằng hai phương pháp này.

Hiện tại, phương pháp vận chuyển hơi vật lý (PVT) là phương pháp trưởng thành nhất trong số tất cả các kỹ thuật phát triển SiC để nuôi cấy tinh thể SiC. Phương pháp là cho chất nền hạt SiC vào chén chứa nguyên liệu bột SiC, sau đó nung chén bằng cảm ứng tần số trung bình hoặc lò điện trở để làm cho nhiệt độ đạt trên 2000 ℃, và các phân tử khí chứa Si và C được tạo ra bởi gradient nhiệt độ giữa nguyên liệu thô và hạt SiC, chuyển sang phiến hạt để phát triển tinh thể SiC. Sự khác biệt đáng kể giữa phương pháp PVT và phương pháp Lely sơ khai là phương pháp PVT đưa vào tinh thể hạt, cải thiện khả năng kiểm soát của quá trình tăng trưởng kết tinh tinh thể hạt và thích hợp để nuôi cấy đơn tinh thể SiC kích thước lớn.

Để biết thêm thông tin, vui lòng liên hệ với chúng tôi qua email victorchan@powerwaywafer.com và powerwaymaterial@gmail.com.