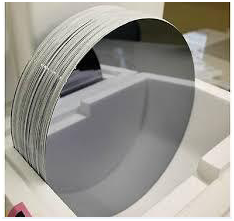

Epitaxy Silicon wafer

Silicon Epiticular Wafer (Epi Wafer) là một lớp tinh thể silicon epiticular được lắng đọng trên một tấm wafer silicon tinh thể đơn (lưu ý: có thể phát triển một lớp lớp Silicon đa tinh thể trên một tấm wafer silicon đơn tinh thể có độ pha tạp cao, nhưng nó cần lớp đệm (như oxit hoặc poly-Si) ở giữa chất nền Si số lượng lớn và lớp silicon epiticular trên cùng. Nó cũng có thể được sử dụng cho bóng bán dẫn màng mỏng.

- Sự miêu tả

Mô Tả Sản Phẩm

Epitaxy Silicon wafer

Silicon epitaxy Wafer(Epi Wafer)là một lớp tinh thể đơn silicon epiticular lắng đọng trên một tinh thểwafer silicon(lưu ý: có thể phát triển một lớp lớp Silicon đa tinh thể trên một tấm wafer silicon đơn tinh thể có độ pha tạp cao, nhưng nó cần lớp đệm (chẳng hạn như oxit hoặc poly-Si) ở giữa chất nền Si số lượng lớn và lớp epiticular trên cùng lớp silicon.Nó cũng có thể được sử dụng cho bóng bán dẫn màng mỏng.

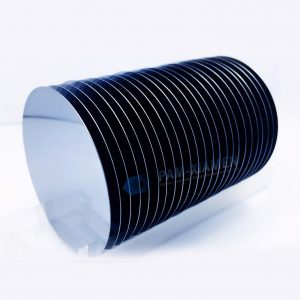

Các phương pháp chuẩn bị tấm silicon epiticular bao gồm epit Wax pha hơi, epit Wax pha lỏng, epit Wax chùm phân tử, v.v. Trong số đó, epit Wax pha hơi dựa trên lắng đọng hơi hóa học (CVD) là quá trình tăng trưởng epiticular silicon chính. Các nguồn thường được sử dụng là SiCl4, SiHCl3, SiH2Cl2 và SiH4.

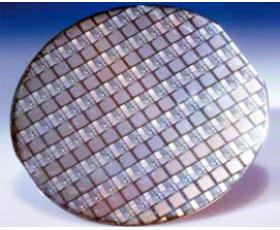

Để đáp ứng nhu cầu của các thiết bị bán dẫn khác nhau, nhiều công nghệ epiticular silicon khác nhau đã được tạo ra để sản xuất tấm wafer silicon epiticular. Ngoài sự phát triển epiticular silicon trong epit Wax ở nhiệt độ thấp và epit Wax giảm áp suất, còn có epitaxy chọn lọc lắng đọng một lớp epiticular silicon trên một phần cụ thể của tấm wafer silicon.

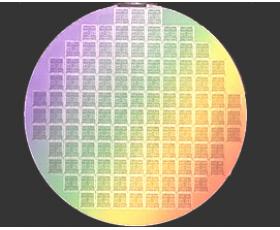

Các lớp epitaxy có thể được pha tạp, vì nó được gửi, để nồng độ doping chính xác trong khi tiếp tục cấu trúc tinh thể của chất nền.

Epilayer trở suất: <1 ohm-cm lên đến 150 ohm-cm

Epilayer độ dày: <1 um lên đến 150 um

Cấu trúc: N / N +, N / N / N +, N / P / N +, N / N + / P-, N / P / P +, P / P +, P- / P / P +.

Ứng dụng wafer: Digital, Linear, Power, MOS, BiCMOS Thiết bị.

lợi thế của chúng tôi trong nháy mắt

1. Thiết bị tăng trưởng epiticular tiên tiến, thiết bị kiểm tra và công nghệ silicon epiticular.

2.Offer chất lượng cao nhất với mật độ khuyết tật thấp và độ nhám bề mặt tốt.

3.Strong hỗ trợ nhóm nghiên cứu và hỗ trợ kỹ thuật cho khách hàng của chúng tôi

6 "(150mm) Wafer đặc điểm kỹ thuật:

| Mục | Đặc điểm kỹ thuật | |

| bề mặt | Sub đặc tả số | |

| Phương pháp phát triển phôi | CZ | |

| loại dẫn | N | |

| dopant | Như | |

| Sự định hướng | (100) ± 0,5 ° | |

| Điện trở | ≤0.005Ohm.cm | |

| RRG | ≤15% | |

| [Oi] Nội dung | 8 ~ 18 ppma | |

| Đường kính | 150 ± 0,2 mm | |

| Tiểu Chiều dài phẳng | 55 ~ 60 mm | |

| Tiểu Flat Location | {110} ± 1 ° | |

| Chiều dài Thứ hai Flat | bán | |

| Thứ hai Flat Location | bán | |

| Độ dày | 625 ± 15 um | |

| Backside Đặc điểm: | ||

| 1, BSD / Poly-Si (A) | 1.BSD | |

| 2, SiO2 | 2.LTO: 5000 ± 500 A | |

| 3, Edge Exclusion | 3.EE:?0.6 mm | |

| Laser Marking | KHÔNG AI | |

| bề mặt phía trước | Đánh bóng mặt kính | |

| Epi | Kết cấu | N / N + |

| dopant | Phos | |

| Độ dày | 3 ± 0,2 um | |

| Thk.Uniformity | ≤5% | |

| Chức vụ đo lường | Trung tâm (1 pt) 10mm từ mép (4 điểm @ 90 độ) | |

| Phép tính | [Tmax-Tmin] ÷ [[Tmax + Tmin] X 100% | |

| Điện trở | 2,5 ± 0,2 Ohm.cm | |

| Res.Uniformity | ≤5% | |

| Chức vụ đo lường | Trung tâm (1 pt) 10mm từ mép (4 điểm @ 90 độ) | |

| Phép tính | [Rmax-Rmin] ÷ [[Rmax + Rmin] X 100% | |

| Ngăn xếp Mật độ lỗi | ≤2 (ea / cm2) | |

| Sương mù | KHÔNG AI | |

| vết trầy xước | KHÔNG AI | |

| Hố, Orange Peel, | KHÔNG AI | |

| cạnh Thái | ≤1 / 3 Epi dày | |

| Trượt (mm) | Tổng chiều dài ≤ 1Dia | |

| Vấn đề nước ngoài | KHÔNG AI | |

| Trở lại nhiễm bẩn bề mặt | KHÔNG AI | |

| Tổng số khiếm khuyết Point (hạt) | ≤30@0.3um |

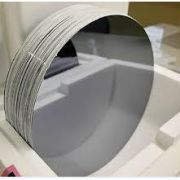

Tấm wafer silicon EPI 4 inch-6

Tấm wafer silicon epiticular 4 inch

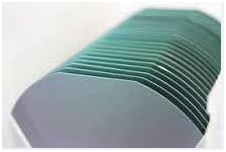

Tăng trưởng epit Wax silicon với Boron Dopant của VPE

Tấm wafer silicon cho ống dẫn sóng quang học tích hợp