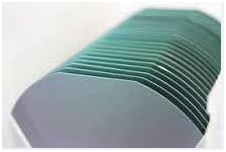

PAM-XIAMEN có thể cung cấp tấm wafer silicon thử nghiệm 4 inch với một mặt được đánh bóng. Các thông số cho tấm wafer 4 ″ -SSP Si ở cấp thử nghiệm như sau:

1. Các thông số của Si đơn tinh thể Wafer ở cấp thử nghiệm

Tấm wafer PAM-210310-Si

| SI. Không | Mục | Đặc tính kỹ thuật |

| 1 | Phương pháp trồng trọt | CZ |

| 2 | wafer Đường kính | 100 ± 0,5 mm |

| 3 | Độ dày Wafer | 525 ± 25 μm |

| 4 | Định hướng bề mặt Wafer | <100> ± 0,5º |

| 5 | Loại | Loại P |

| 6 | dopant | Boron |

| 7 | Mật độ xáo trộn | Dưới 5000 / cm2 |

| 8 | Điện trở | 2-8 Ohm-cm |

| 9 | Biến đổi điện trở suất xuyên tâm (tối đa) | N / A |

| 10 | Độ phẳng | |

| 10a | BOW (tối đa) | 50 μm |

| 10b | TIR | N / A |

| 10c | TTV | 10 μm |

| 10 ngày | LÀM CONG | N / A |

| 11 | Căn hộ chính | |

| 11a | Chiều dài | 32,5 ± 2,5 mm |

| 11b | Sự định hướng | (110) ± 0,2º theo Tiêu chuẩn SEMI |

| 11c | Căn hộ thứ cấp | Theo tiêu chuẩn SEMI |

| 12 | Kết thúc bề mặt trước | Đánh bóng mặt kính |

| 13 | Tối đa các hạt có kích thước ≥0,3μm | <30 cái |

| 14 | Trầy xước, khói mù, chip cạnh, vỏ cam & các khuyết tật khác | N / A |

| 15 | Mặt sau | Khắc |

| 16 | Yêu cầu đóng gói | băng wafer |

2. Future Development of Test Grade Silicon Wafer

Silicon đơn tinh thể có độ tinh khiết cao là một vật liệu bán dẫn quan trọng. Chất bán dẫn silicon loại p có thể được tạo ra bằng cách thêm một lượng nhỏ nguyên tố nhóm IIIA vào silicon đơn tinh thể; một lượng nhỏ các nguyên tố nhóm VA được thêm vào để tạo thành chất bán dẫn loại n. Chất bán dẫn loại p và chất bán dẫn loại n được kết hợp với nhau để tạo thành tiếp giáp pn. Ngoài ra, các điốt, triode, thyristor, bóng bán dẫn hiệu ứng trường và các mạch tích hợp khác nhau (bao gồm cả chip và CPU trong máy tính) đều được làm bằng silicon. Lớp thử nghiệm wafer silicon là một vật liệu đầy hứa hẹn trong việc phát triển năng lượng.

Hiện tại, ngành công nghiệp quang điện vẫn bị chi phối bởi các tấm silicon loại P. Các tấm silicon loại P được pha tạp chất với boron. Hệ số phân tách của bo và silicon là tương đương, và độ đồng nhất phân tán dễ kiểm soát. Do đó, quá trình sản xuất đơn giản, và chi phí thấp hơn, nhưng hiệu quả cao nhất có một hạn chế. Các tấm silicon loại N được pha tạp chất với phốt pho và khả năng tương thích của phốt pho với silicon rất kém. Sự phân bố của phốt pho không đồng đều khi que được rút ra, và quá trình này phức tạp hơn. Tuy nhiên, tấm silicon loại thử nghiệm loại N thường có tuổi thọ cao hơn và hiệu quả sử dụng pin có thể cao hơn. Việc cải thiện hiệu suất đề cập đến việc cải thiện hiệu suất chuyển đổi quang điện. Vì vậy, trong tương lai, sự phát triển công nghệ của tấm silicon chủ yếu dựa trên việc nâng cao hiệu quả và giảm chi phí.

Để biết thêm thông tin, vui lòng liên hệ với chúng tôi qua email victorchan@powerwaywafer.com và powerwaymaterial@gmail.com.