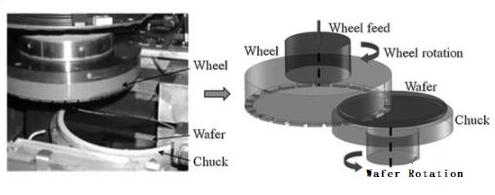

Từ góc độ cấu trúc mặt cắt ngang của mạch tích hợp, hầu hết các mạch tích hợp được chế tạo trên lớp bề mặt nông của vật liệu nền silicon. Do các yêu cầu của quy trình sản xuất, các yêu cầu cao được đặt ra đối với độ chính xác về kích thước, độ chính xác về hình học, độ sạch bề mặt và cấu trúc mạng vi mô bề mặt của wafer. Do đó, trong hàng trăm dòng quy trình, không thể sử dụng các tấm mỏng hơn và chỉ các tấm wafer có độ dày nhất định mới có thể được sử dụng để truyền và băng ra trong quá trình này. Thông thường, trước khi mạch tích hợp được đóng gói, cần phải loại bỏ một độ dày nhất định ở mặt sau của đế wafer. Quá trình này được gọi là quá trình làm mỏng mặt sau wafer. Làm mỏng wafer còn được gọi là mài wafer. Các công nghệ làm mỏng wafer hiện có chủ yếu bao gồm mài bàn quay và làm mỏng wafer tự quay.

Quy trình làm mỏng wafer thông thường có thể đạt đến mức sau:

Làm mỏng/đánh bóng đến 80-100um

Độ nhám: 5-20nm

Độ phẳng: ±3um

PAM-XIAMEN có thể cung cấpGaAs siêu mỏngđể đáp ứng nhu cầu của bạn.

Quy trình làm mỏng wafer

Chức năng của quá trình làm mỏng wafer là nghiền vật liệu nền mặt sau của wafer chức năng (chủ yếu là wafer silicon) để loại bỏ độ dày nhất định của vật liệu. Nó có lợi cho các yêu cầu của quy trình đóng gói tiếp theo và các yêu cầu về độ bền vật lý, tản nhiệt và kích thước của chip.

Ngoài ra, việc làm mỏng wafer có những ưu điểm sau đối với chip:

1) Hiệu quả tản nhiệt sẽ được cải thiện đáng kể. Khi cấu trúc chip ngày càng phức tạp, độ tích hợp ngày càng cao và số lượng bóng bán dẫn tăng mạnh, tản nhiệt dần trở thành yếu tố chính ảnh hưởng đến hiệu suất và tuổi thọ của chip. Chip mỏng sẽ tốt hơn cho việc tản nhiệt từ đế.

2) Giảm kích thước của gói chip, nhưng tăng tỷ lệ khối lượng chức năng hiệu dụng. Các sản phẩm vi điện tử ngày càng phát triển theo hướng nhẹ, mỏng và ngắn nên việc giảm độ dày cũng đồng nghĩa với việc giảm kích thước chip theo.

3) Giảm ứng suất bên trong của chip. Chiều dày chip càng dày thì ứng suất bên trong sinh ra ở mặt sau chip do nhiệt sinh ra trong quá trình làm việc của chip. Nhiệt độ của chip tăng lên và chênh lệch nhiệt giữa các lớp đế tăng lên, điều này làm tăng ứng suất bên trong của chip và ứng suất bên trong lớn sẽ khiến chip bị nứt.

4) Cải thiện hiệu suất điện. Độ dày của wafer càng mỏng, mặt phẳng tiếp đất càng gần lớp mạ vàng mặt sau thì hiệu suất tần số cao của thiết bị càng tốt

5) Cải thiện năng suất chế biến hạt lựu. Làm mỏng tấm wafer bán dẫn có thể giảm khối lượng xử lý trong quá trình đóng gói và cắt hạt lựu, tránh các khuyết tật như sứt mẻ trong miếng cắt hạt lựu và giảm khả năng hư hỏng chip.

Để biết thêm thông tin, xin vui lòng liên hệ với chúng tôi email tạivictorchan@powerwaywafer.com và powerwaymaterial@gmail.com.