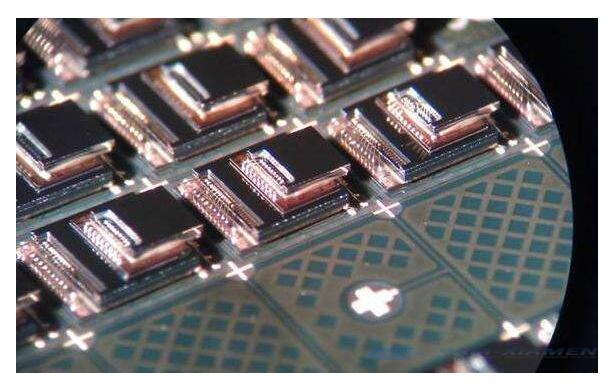

PAM-Hạ Môn tham gia thiết kế và xử lý MEMS và các thiết bị vi mạch tích hợp vi sóng GaAs bán dẫn hợp chất (GaAs MMIC), đồng thời tập trung vào nghiên cứu, phát triển, sản xuất và dịch vụ cảm biến micro-nano, hệ thống cơ điện tử vi mô (MEMS), sản xuất micro-nano và chip GaAs bán dẫn hợp chất. Chúng tôi là một doanh nghiệp công nghệ cao cung cấp dịch vụ xử lý wafer, chuyên nghiên cứu, phát triển và sản xuất cảm biến MEMS (Hệ thống cơ điện vi mô) và có năng lực thiết kế và xử lý micro-nano ở trình độ tiên tiến quốc tế. Chúng tôi có thể nhận ra quá trình sản xuất, đóng gói và thử nghiệm các loại cảm biến MEMS khác nhau. Các sản phẩm được phát triển bằng quy trình bán dẫn wafer bao gồm đầu dò hồng ngoại không được làm mát, cảm biến áp suất, vi lỏng, cảm biến khí và các cảm biến MEMS khác. Các sản phẩm mạch tích hợp GaAs bán dẫn phức hợp bao gồm công suất bóng bán dẫn có độ linh động cao (pHEMT) không tiếp xúc căng thẳng, tiếng ồn thấp và công tắc quang dẫn GaAs và các dịch vụ xử lý chip khác.

Bên cạnh đó, PAM-XIAMEN với tư cách là một trong những công ty gia công wafer đảm nhận sản xuất và các dịch vụ xử lý một bước và nhiều bước của các thiết bị bán dẫn khác nhau như MEMS và GaAs, chẳng hạn như oxy hóa nhiệt wafer silicon, cấy ion, quang khắc, khắc RIE, PECVD , LPCVD, phún xạ magnetron, bốc hơi chùm điện tử, khắc sâu silicon, ủ nhanh, mạ điện, cắt, liên kết, đóng gói và các loại khác dịch vụ đúc wafer. Cung cấp các loại wafer silicon, wafer đánh bóng đơn / đôi, wafer silicon oxit, wafer tráng, wafer siêu dày, wafer oxit siêu dày, wafer mạ kim loại, wafer cắt, wafer GaAs & GaP, GaN wafers, sapphire wafers, Vân vân.

Sau đây là các dịch vụ của quá trình wafer to chip do chúng tôi cung cấp:

1. Dịch vụ tích hợp vật liệu hai chiều MEMS

Các kỹ thuật xử lý wafer của chúng tôi có thể nhận ra việc chuyển vật liệu hai chiều trên MEMS.

2. Dịch vụ xử lý cho MEMS và băng ra bán dẫn

Có thể cung cấp các dịch vụ phát triển quy trình và đầu ra của chip bán dẫn (ví dụ: DMOS; L-IGBT; MOSFET; PHEMT; HFET; Diode SiC; chip tần số vô tuyến SiC, v.v.)

Cũng có sẵn các dịch vụ phát triển quy trình và trích xuất các chip MEMS (microfluidics / cảm biến khí / cảm biến áp suất, v.v.).

3. Quy trình Polyimide

Polyimide (PI) được làm từ pyromellitic dianhydride (PMDA) và diaminodiphenyl ete (DDE) trong dung môi phân cực mạnh thông qua quá trình polycondensation và đúc thành màng, sau đó được ngâm hóa. Polyimide có khả năng chịu nhiệt độ cao và thấp tuyệt vời, cách điện, độ bám dính, độ bền điện môi, tính chất cơ học và khả năng chống bức xạ. Nó có thể được sử dụng trong thời gian dài trong khoảng nhiệt độ -269 ℃ -280 ℃, và có thể đạt đến nhiệt độ cao 400 ℃ trong thời gian ngắn. Chúng tôi nắm vững hai loại công nghệ xử lý thiết bị là màng khô PI và keo PI nhằm mang đến cho khách hàng những dịch vụ kỹ thuật chất lượng cao.

3.1 Ứng dụng Công nghệ Xử lý Wafer Polyimide

Là một vật liệu kỹ thuật đặc biệt, polyimide được sử dụng rộng rãi trong hàng không, vũ trụ, vi điện tử, nanomet, tinh thể lỏng, màng ngăn cách, laser và các lĩnh vực khác.

3.2 Khả năng dịch vụ xử lý PI

Màng khô: độ dày 20-150um, độ sâu ăn mòn ≤15um;

Giải pháp cảm quang: độ rộng vạch tối thiểu 5um, độ dày 5-20um;

Dung dịch không cảm quang: độ sâu khắc 0-15um.

3.3 Ưu điểm của Dịch vụ Xử lý PI

Chúng tôi có công nghệ xử lý màng khô & keo PI, độ sâu ăn mòn màng khô có thể đạt tới 15um, và quy trình xếp chồng màng PI nhiều lớp thành thạo, độ bám dính tốt.

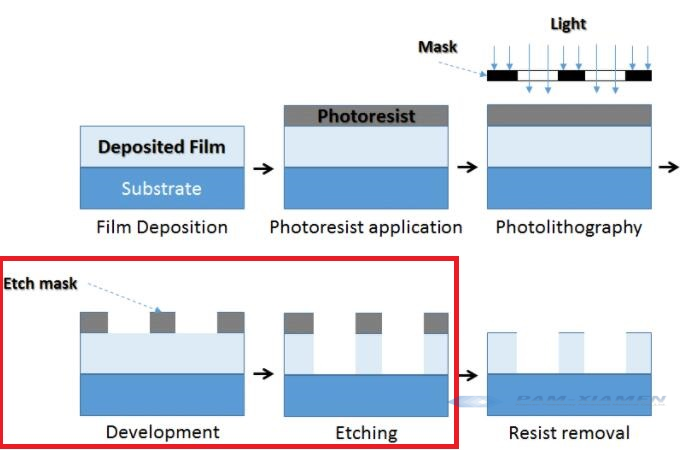

4. Quy trình khắc Wafer

Etch là công nghệ khắc có chọn lọc bề mặt đế bán dẫn hoặc màng phủ bề mặt theo mẫu mặt nạ hoặc yêu cầu thiết kế. Đây là một trong những bước rất quan trọng của quy trình sản xuất wafer bán dẫn, quy trình sản xuất vi mạch điện tử và quy trình sản xuất micro-nano. Nó là một trong những giải pháp xử lý wafer chính của xử lý mẫu liên quan đến quang khắc. Servcie xử lý khắc được chia thành khắc khô và khắc ướt. PAM-XIAMEN hiện làm chủ nhiều quy trình khắc và sẽ thiết kế các giải pháp khắc với hiệu ứng khắc tốt và tiết kiệm chi phí theo nhu cầu của khách hàng.

Khắc trong quy trình chế tạo Wafer bán dẫn

4.1 Ứng dụng công nghệ khắc

Công nghệ khắc của chúng tôi chủ yếu được sử dụng trong quá trình xử lý các thiết bị bán dẫn, sản xuất mạch tích hợp, mạch màng mỏng, mạch in và các mẫu đẹp khác.

4.2 Khả năng xử lý khắc

Công nghệ khắc: khắc chùm ion, khắc sâu silicon, khắc ion phản ứng, chùm ion tập trung và các công nghệ khắc khác;

Vật liệu khắc: silic, oxit silic, nitrit silic, kim loại, thạch anh và các vật liệu khác

4.3 Ưu điểm của dịch vụ khắc của chúng tôi

* Thành thạo một loạt các kỹ thuật khắc;

* Nhiều loại vật liệu khắc;

* Tỷ lệ khung hình tối đa của khắc sâu silicon là 20: 1 với độ chính xác khắc cao và độ rộng đường nhỏ.

5. Dịch vụ gia công lớp phủ

Phủ chân không là sự lắng đọng của một kim loại hoặc phi kim loại nhất định trên bề mặt vật liệu dưới dạng pha khí trong môi trường chân không để tạo thành màng dày đặc. Chất lượng của lớp phủ rất quan trọng đối với sự hình thành chức năng của các thiết bị bán dẫn.

5.1 Ứng dụng công nghệ sơn

Xử lý Wafer kim loại chủ yếu được sử dụng trong quá trình sản xuất các thiết bị bán dẫn nano siêu nhỏ. Vật liệu kim loại và ITO chủ yếu được sử dụng để chuẩn bị điện cực, và các vật liệu phi kim loại khác chủ yếu được sử dụng để chuẩn bị các lớp điện môi cách điện và các lớp mặt nạ hy sinh.

5.2 Khả năng xử lý lớp phủ

Công nghệ phủ chính: phún xạ magnetron bay hơi chùm điện tử, LPCVD, PECVD, ALD, MOCVD và MBE.

5.3 Vật liệu phủ

Chúng tôi có thể sơn phủ bằng các vật liệu sau:

Kim loại: Ti, Al, Ni, Au, Ag, Mo, Cr, Pt, Cu, Ta, TiW, Pd, Zn, W, Nb;

Phi kim loại: Si, SiO2, SiNx, TiN, Ga2O3, Al2O3, TiO2, HfO2, MgF2, ITO, Ta2O5;

Phim Piezo: AlN, PZT, ZnO;

Lớp nền: tấm silicon, phiến thủy tinh thạch anh, phiến đá sapphire, cacbua silic, Chất nền nhóm II-IIII, chất nền nhóm III-V, PET, Pi, v.v.

5.4 Ưu điểm của dịch vụ gia công lớp phủ

* Làm chủ nhiều công nghệ sơn và nhiều loại vật liệu phủ.

* Phạm vi độ dày lớp phủ: 5nm-10um;

* Kích thước cơ bản là 8 inch tương thích trở xuống. Độ đồng đều của lớp phủ tốt và lớp phủ dày đặc.

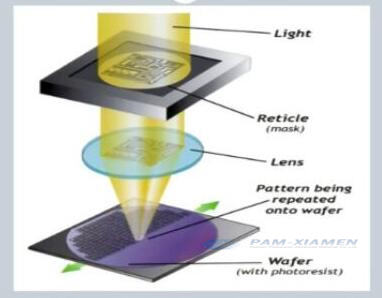

6.Xử lý quang khắc

Quang khắc là một công đoạn quan trọng trong quy trình sản xuất các thiết bị bán dẫn. Cấu trúc thiết bị được mô tả trên lớp cản quang bằng cách tiếp xúc và phát triển, sau đó hoa văn trên mặt nạ được chuyển sang chất nền thông qua quá trình ăn mòn. Chúng tôi hiện đang sở hữu các bước xử lý wafer thạch bản khác nhau, chẳng hạn như kỹ thuật in thạch bản chùm điện tử, phép in thạch bản từng bước, và phép in thạch bản tiếp xúc.

Xử lý Wafer Photolithography

6.1 Ứng dụng công nghệ in thạch bản

Công nghệ in thạch bản được sử dụng chủ yếu trong quá trình sản xuất các thiết bị bán dẫn và mạch tích hợp.

6.2 Khả năng xử lý Wafer của Photolithography

EBL (Electron Beam Lithography): Giá trị CD tối thiểu là 50nm và độ chính xác có thể đạt 10%.

Bước: giá trị CD tối thiểu là 350nm, sai số phơi sáng là ± 0,1um và vùng phơi sáng tối đa là 6 inch.

In thạch bản tiếp xúc và gần: Máy in thạch bản SUSS MA6 / BA6, giá trị CD tối thiểu 2um, sai số phơi sáng ± 0,3um

6.3 Ưu điểm của Photolithography

* Tùy chỉnh giải pháp in thạch bản tiết kiệm chi phí nhất theo nhu cầu của khách hàng;

* Độ chính xác cao và độ rộng dòng nhỏ;

* Kích thước bề mặt từ 1 cm đến 8 inch;

* Độ trung thực đồ họa cao.

7. Công nghệ TSV

Công nghệ TSV là tên viết tắt của công nghệ thông qua silicon, là một giải pháp xử lý wafer tiên tiến để xếp chồng các chip trong mạch tích hợp ba chiều để đạt được kết nối với nhau. Bởi vì dịch vụ xử lý TSV có thể tối đa hóa mật độ xếp chồng của chip theo hướng ba chiều, đường kết nối ngắn nhất giữa các chip, kích thước nhỏ nhất và cải thiện đáng kể hiệu suất của tốc độ chip và tiêu thụ điện năng thấp, nó trở nên bắt mắt nhất một trong công nghệ đóng gói cấp wafer điện tử hiện tại.

Do những hạn chế của quá trình co ngót và vật liệu có giá trị điện môi thấp, công nghệ xếp chồng 3D được coi là chìa khóa cho khả năng sản xuất chip hiệu suất cao với kích thước nhỏ hơn, và thông qua vias silicon (TSV) có thể tích hợp việc xếp wafer thông qua dẫn truyền thẳng đứng. Đạt được kết nối mạch giữa các chip giúp cải thiện sự tích hợp và hiệu quả của các hệ thống xử lý tấm wafer với chi phí thấp hơn và là một cách quan trọng để thực hiện tích hợp 3D của các mạch tích hợp. Chúng tôi có một quy trình TSV hoàn chỉnh để đáp ứng yêu cầu của bạn về kết nối chip.

8. Công nghệ ăn mòn

PAM-XIAMEN cung cấp dịch vụ ăn mòn, bao gồm ôxít, nitride, silicon, polysilicon và ăn mòn đẳng hướng germani, ăn mòn kim loại tiêu chuẩn, môi trường cách điện không tiêu chuẩn, ăn mòn kim loại và bán dẫn, loại bỏ quang điện tử và các bước làm sạch wafer silicon, ăn mòn silicide, nhựa và polyme ăn mòn, ăn mòn không đẳng hướng silicon, ăn mòn silicon số lượng lớn và silicon germani tự dừng, ăn mòn điện hóa và tự dừng, ăn mòn có hỗ trợ quang học và tự dừng, tự dừng ăn mòn màng mỏng, loại bỏ lớp hy sinh, hình thành silicon xốp.

9. Công nghệ liên kết Wafer

Liên kết là một công nghệ trong đó hai mảnh vật liệu bán dẫn đồng nhất hoặc không đồng nhất có bề mặt phẳng sạch và cấp nguyên tử trải qua các xử lý làm sạch và kích hoạt bề mặt, và được liên kết trực tiếp trong một số điều kiện nhất định. Các tấm wafer được liên kết với nhau thông qua lực van der Waals, lực phân tử hoặc thậm chí là lực nguyên tử. Chúng tôi cung cấp dịch vụ xử lý liên kết từ chip đến tấm wafer như sau:

- Liên kết anốt (thủy tinh pyrex và tấm silicon);

- Liên kết eutectic (PbSn, AuSn, CuSn, AuSi, v.v.), chất hàn được cung cấp bởi khách hàng;

- Keo liên kết (AZ4620, SU8), Keo chuyên dụng liên kết);

- Liên kết dây và các loại khác.

10. Công nghệ đóng gói

PAM-XIAMEN cung cấp dịch vụ xử lý đóng gói nhanh các chip kỹ thuật MPW. Các loại bao bì bao gồm niêm phong nhanh COB, niêm phong nhanh gói gốm và niêm phong nhanh gói nhựa, bao gồm nhưng không giới hạn các loại gói sau DIP, SOP, TSSOP, SOT, TO, QFN, DFN, LGA, COB, BGA, QFP, LCC , Vân vân.

Có thể thực hiện dịch vụ gia công bao bì kín khí như hàn AuSn và hàn đường nối song song của vỏ gốm. Mài chip, đánh bóng, cắt lưỡi cơ khí, cắt không đánh dấu bằng laser wafer silicon, liên kết dây vàng, hàn laser, gắn chip, lớp phủ pha chế, hàn nóng lại, hàn chip lật, hàn niêm phong song song, cấy bi BGA, lực cắt kéo kiểm tra, kiểm tra SEM bằng kính hiển vi điện tử quét, kiểm tra tia X-Ray, kiểm tra không phá hủy bằng siêu âm và kiểm tra độ nhám bề mặt, v.v.

11. Công nghệ phát hiện

Chúng tôi có nhiều công nghệ phát hiện, bao gồm TEM, SEM, XRD, AFM, XPS, XRD, kính hiển vi siêu âm, tia X, máy đo bước, máy đo độ dày màng, máy đo độ dày màng, Raman, v.v.

Để biết thêm thông tin, vui lòng liên hệ với chúng tôi qua email victorchan@powerwaywafer.com và powerwaymaterial@gmail.com.