PAM-XIAMEN pode fornecer wafers epitaxiais de SiC, mais especificações de wafer, leia:https://www.powerwaywafer.com/sic-wafer/sic-epitaxy.html.

Embora os wafers epitaxiais de SiC apresentem excelentes características em dispositivos de alta tensão e alta corrente, ainda existem vários tipos de defeitos que têm um impacto negativo no desempenho elétrico dos dispositivos de SiC. Entre eles, os poços superficiais têm impacto em diferentes tipos de dispositivos SiC, como SBD e MOS. Poços superficiais no wafer de SiC farão com que as características do dispositivo se deteriorem devido à aglomeração do campo elétrico. Estudiosos mostraram que poços superficiais geram corrente de fuga no SBD, mas a causa e o mecanismo de formação dos poços superficiais ainda não são claros. Portanto, é significativo estudar os efeitos dos parâmetros de crescimento primitivo e epitaxial nas pontuações superficiais.

1.Eefeito deGfilaTtemperatura ligadaSuperfície Psuade Epitaxia 4H-SiC

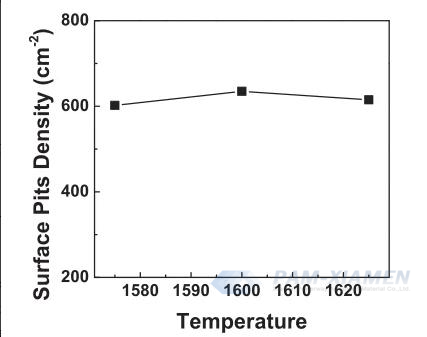

Primeiramente, foi estudada a influência da temperatura de crescimento na densidade superficial da cava. Sob a condição de uma relação C/Si de 1,05, as temperaturas de crescimento epitaxial do 4H-SiC são 1575, 1600 e 1625 ℃, respectivamente. Como mostrado na Fig. 1, a temperatura epitaxial não tem efeito significativo na densidade da depressão. A densidade dos defeitos de fusão não mostra uma tendência decrescente significativa com as mudanças de temperatura. Se a temperatura continuar a subir ou descer, causará outros problemas, como defeitos triangulares e agrupamento escalonado.

Fig.1 Efeito da temperatura de crescimento nas pontuações superficiais da epitaxia de SiC

2. Influência deC/SiRação ativadaSiC Epitaxial Sseu rostoPsua

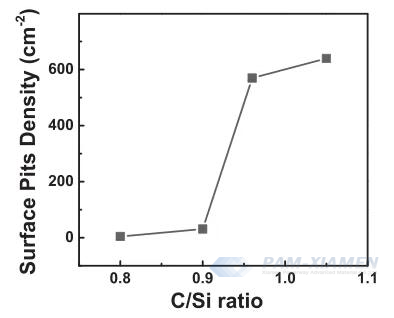

Em seguida, foi estudado o efeito da relação C/Si na densidade superficial da cava. Como mostrado na Fig. 2, a densidade dos poços superficiais diminui com a diminuição da relação C/Si. Quando a relação C/Si aumenta para 1,05, a densidade de pites aumenta ainda mais, enquanto quando a relação C/Si diminui para 0,9, a densidade de pites diminui rapidamente para cerca de 30/cm2. Os resultados são semelhantes a pesquisas anteriores. Quando a relação C/Si é alta, uma atmosfera rica em C é propícia à formação de fossas superficiais, e a forma das fossas superficiais gradualmente forma fossas profundas. No entanto, quando a relação C/Si é muito baixa, pode causar um aumento na concentração de fundo e uma diminuição no Si. Portanto, é necessário procurar outros parâmetros para suprimir ainda mais a densidade superficial do poço de SiC. Com base em uma relação C/Si de 0,9, continue a otimizar a densidade do poço do wafer 4H-SiC Epi.

Fig. 2 Influência da relação C/Si nas pontuações superficiais epitaxiais de 4H-SiC

3. Cl/SiRaçãoImpactosobreSseu rostoPé deEpicamada 4H-SiC

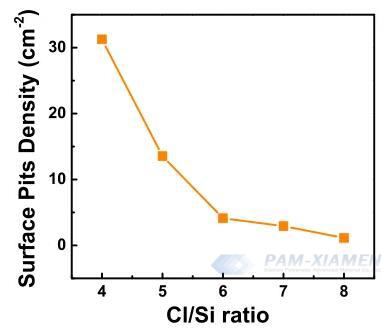

Investigações adicionais foram conduzidas sobre o efeito da relação Cl/Si nas pontuações superficiais, com uma relação C/Si de 0,9, como mostrado na Fig. 3. À medida que a relação Cl/Si aumenta, a densidade das pontuações superficiais diminui. Quando a relação Cl/Si é 8, a densidade das cavidades superficiais diminui para 1 cm-2. À medida que a relação Cl/Si aumenta, os átomos de Cl podem efetivamente reduzir a nucleação uniforme dos átomos de Si, formando um ambiente rico em Si na superfície do chip. Portanto, a relação efetiva C/Si na superfície do substrato foi reduzida, o crescimento do fluxo escalonado foi aumentado e a formação de defeitos semelhantes a poços foi suprimida.

Fig. 3 Impacto da relação Cl/Si nas pontuações superficiais epitaxiais de 4H-SiC

Durante o processo de crescimento epitaxial do 4H-SiC, a relação C/Si e a relação Cl/Si têm um impacto significativo nas pontuações superficiais. Uma relação C/Si mais baixa e uma relação Cl/Si mais alta formarão um ambiente rico em silício na superfície do wafer durante o processo de crescimento, o que é crucial para reduzir poços superficiais em wafers epitaxiais 4H-SiC. Ao otimizar o processo, a densidade do poço foi reduzida para menos de 1/cm2, e a densidade de defeitos fatais de superfície (incluindo defeitos triangulares, defeitos de cenoura, quedas, etc.) foi garantida dentro de uma determinada faixa, obtendo wafers epitaxiais de SiC de alta qualidade, atendendo aos requisitos dos dispositivos de energia de SiC.

Para mais informações, entre em contato conosco pelo e-mailvictorchan@powerwaywafer.com e powerwaymaterial@gmail.com.