PAM-XIAMEN は SiC エピタキシャル ウェーハを供給できます。ウェーハ仕様の詳細については、以下をお読みください。https://www.powerwaywafer.com/sic-wafer/sic-epitaxy.html.

SiC エピタキシャル ウェーハは高電圧および大電流デバイスにおいて優れた特性を示しますが、SiC デバイスの電気的性能に悪影響を与えるいくつかの種類の欠陥が依然として存在します。 その中でも、表面ピットは、SBD や MOS などのさまざまな種類の SiC デバイスに影響を与えます。 SiC ウェーハの表面にピットがあると、電界集中によりデバイス特性が劣化します。 学者らは、表面ピットが SBD の漏れ電流を生成することを示しましたが、表面ピットの原因と形成メカニズムはまだ不明です。 したがって、表面ピットに対するプリミティブ成長パラメータとエピタキシャル成長パラメータの影響を研究することは重要です。

1.Eの影響GロウスT気温面Pそれの4H-SiCエピタキシーの

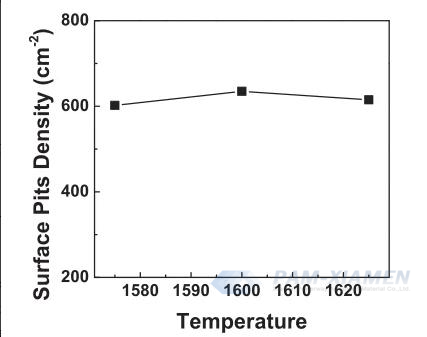

まず、表面ピット密度に対する成長温度の影響を研究した。 C/Si比1.05の条件下では、4H-SiCのエピタキシャル成長温度はそれぞれ1575℃、1600℃、1625℃である。 図1に示すように、エピタキシャル温度はピット密度に大きな影響を与えません。 溶融欠陥の密度は、温度が変化しても顕著な減少傾向を示しません。 温度が上昇または下降し続けると、三角欠陥やステップバンチングなどの別の問題が発生します。

図1 SiCエピタキシーの表面ピットに対する成長温度の影響

2. 影響C/SiR比率オンSiCエピタキシャルS表面Pそれの

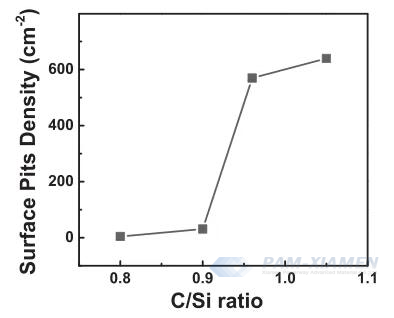

次に、表面ピット密度に対する C/Si 比の影響を研究しました。 図2に示すように、C/Si比が減少すると、表面ピットの密度が減少する。 C/Si比が1.05まで増加するとピット密度はさらに増加しますが、C/Si比が0.9まで減少するとピット密度は30個/cm程度まで急激に減少します。2。 結果は以前の研究と同様です。 C/Si比が高い場合、Cが豊富な雰囲気は表面ピットの形成を促進し、表面ピットの形状は徐々に深いピットを形成する。 しかしながら、C/Si比が低すぎると、バックグラウンド濃度の増加およびSiの減少を引き起こす可能性がある。 したがって、SiC 表面ピット密度をさらに抑制するには、他のパラメータを探索する必要があります。 C/Si比0.9に基づいて、4H-SiC Epiウェーハのピット密度の最適化を継続します。

図2 4H-SiCエピタキシャル表面ピットに対するC/Si比の影響

3. Cl/SiR比率インパクトの上S表面Pそれの4H-SiCエピ層

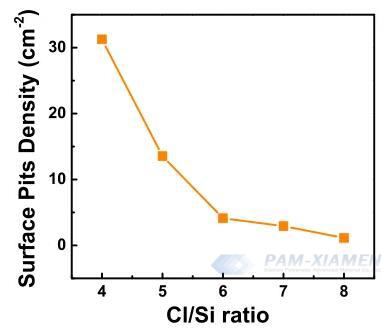

表面ピットに対する Cl/Si 比の影響について、図 3 に示すように C/Si 比を 0.9 としてさらに調査しました。Cl/Si 比が増加するにつれて、表面ピットの密度は減少します。 Cl/Si比が8の場合、表面ピットの密度は1cmに減少します-2。 Cl/Si 比が増加すると、Cl 原子は Si 原子の均一な核生成を効果的に減少させ、チップ表面に Si に富んだ環境を形成します。 したがって、基板表面の実効的なC/Si比が減少し、ステップフロー成長が促進され、ピット状欠陥の形成が抑制されました。

図 3 4H-SiC エピタキシャル表面ピットに対する Cl/Si 比の影響

4H-SiC エピタキシャル成長プロセス中、C/Si 比および Cl/Si 比は表面ピットに大きな影響を与えます。 C/Si 比が低く、Cl/Si 比が高いと、成長プロセス中にウェーハの表面にシリコンが豊富な環境が形成されます。これは、4H-SiC エピタキシャル ウェーハの表面ピットを減らすために重要です。 プロセスの最適化により、ピット密度を1/cm未満に低減2、表面致命欠陥密度(三角欠陥、キャロット欠陥、転倒等を含む)を一定範囲内に確保し、SiCパワーデバイスの要求を満たす高品質なSiCエピタキシャルウェーハが得られました。

詳細については、メールでお問い合わせください。victorchan@powerwaywafer.com と powerwaymaterial@gmail.com.