PAM-XIAMEN can supply SiC epitaxial wafers, more wafer specifications please read: https://www.powerwaywafer.com/sic-wafer/sic-epitaxy.html.

Although SiC epitaxial wafers exhibit excellent characteristics in high-voltage and high current devices, there are still several types of defects that have a negative impact on the electrical performance of SiC devices. Among them, surface pits have an impact on different types of SiC devices such as SBD and MOS. Surface pits on SiC wafer will make the device characteristics deteriorate due to electric field crowding. Scholars have shown that surface pits generate leakage current in SBD, but the cause and formation mechanism of surface pits are still unclear. Therefore, it’s significant to study the effects of primitive and epitaxial growth parameters on surface pits.

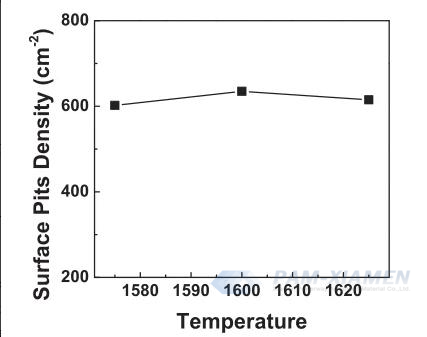

1. Effect of GrowthTemperature onSurface Pits of 4H-SiC Epitaxy

Firstly, the influence of growth temperature on surface pit density was studied. Under the condition of a C/Si ratio of 1.05, the epitaxial growth temperatures of 4H-SiC are 1575, 1600, and 1625 ℃, respectively. As shown in Fig. 1, the epitaxial temperature has no significant effect on the pit density. The density of melt defects does not show a significant downward trend with temperature changes. If the temperature continues to rise or fall, it will cause other problems such as triangular defects and step bunching.

Fig.1 Effect of growth temperature on surface pits of SiC epitaxy

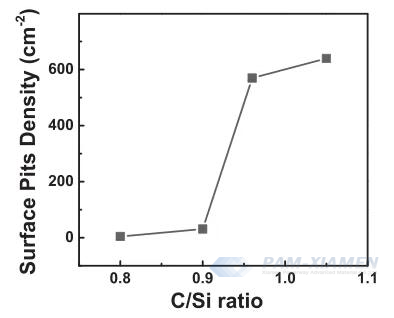

2. Influence of C/Si Ratio on SiC Epitaxial Surface Pits

Then, the effect of C/Si ratio on surface pit density was studied. As shown in Fig. 2, the density of surface pits decreases with the decrease of C/Si ratio. When the C/Si ratio increases to 1.05, the pit density further increases, while when the C/Si ratio decreases to 0.9, the pit density rapidly decreases to around 30/cm2. The results are similar to previous research. When the C/Si ratio is high, a rich C atmosphere is conducive to the formation of surface pits, and the shape of surface pits gradually forms deep pits. However, when the C/Si ratio is too low, it can cause an increase in background concentration and a decrease in Si. Therefore, it is necessary to search for other parameters to further suppress SiC surface pit density. On the basis of a C/Si ratio of 0.9, continue to optimize the pit density of 4H-SiC Epi wafer.

Fig. 2 Influence of C/Si ratio on 4H-SiC epitaxial surface pits

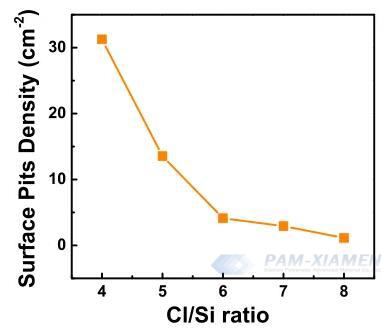

3. Cl/Si Ratio Impact on Surface Pits of 4H-SiC Epilayer

Further investigation was conducted on the effect of Cl/Si ratio on surface pits, with a C/Si ratio of 0.9, as shown in Fig. 3. As the Cl/Si ratio increases, the density of surface pits decreases. When the Cl/Si ratio is 8, the density of surface pits decreases to 1 cm-2. As the Cl/Si ratio increases, Cl atoms can effectively reduce the uniform nucleation of Si atoms, forming a Si rich environment on the chip surface. Therefore, the effective C/Si ratio on the substrate surface was reduced, the step flow growth was enhanced, and the formation of pit like defects was suppressed.

Fig. 3 Cl/Si ratio impact on 4H-SiC epitaxial surface pits

During the 4H-SiC epitaxial growth process, the C/Si ratio and Cl/Si ratio have a significant impact on surface pits. A lower C/Si ratio and a higher Cl/Si ratio will form a silicon rich environment on the surface of the wafer during the growth process, which is crucial for reducing surface pits on 4H-SiC epitaxial wafers. By optimizing the process, the pit density was reduced to below 1/cm2, and the surface fatal defect density (including triangular defects, carrot defects, falls, etc.) was ensured to be within a certain range, obtaining high-quality SiC epitaxial wafers, meeting the requirements of SiC power devices.

For more information, please contact us email at victorchan@powerwaywafer.com and powerwaymaterial@gmail.com.