Il wafer epitassiale SiC è disponibile per la fabbricazione di dispositivi MOSFET, le specifiche del wafer sono disponibili inhttps://www.powerwaywafer.com/sic-mosfet-structure.html

1. fosse epitassiali

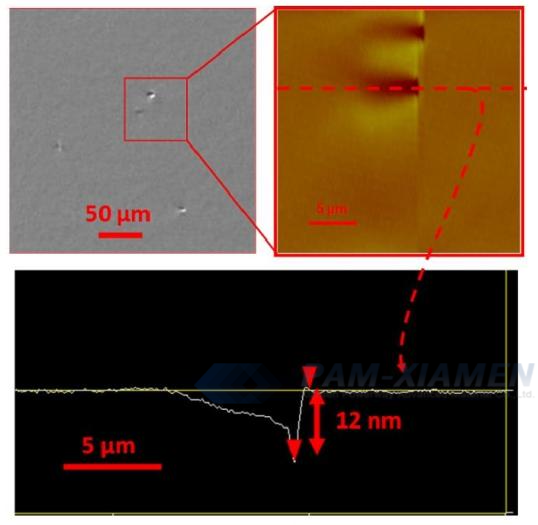

Le cavità epitassiali, essendo uno dei difetti morfologici superficiali più comuni, hanno una morfologia superficiale e un profilo strutturale tipici come mostrato in Fig.1. La posizione dei solchi di corrosione della dislocazione della filettatura (TD) osservata dopo la corrosione KOH sul retro del dispositivo corrisponde in modo significativo alla posizione dei solchi epitassiali prima della preparazione del dispositivo, indicando che la formazione di difetti dei solchi epitassiali è correlata alle dislocazioni della filettatura.

Fig. 1 Diagramma in sezione trasversale dei difetti di cavità epitassiali nello strato epitassiale di SiC

2. Effetti dei difetti del pit epitassiale sul MOSFET SiC

L'influenza dei difetti dei pit epitassiali sulle caratteristiche dei dispositivi MOSFET viene analizzata come segue:

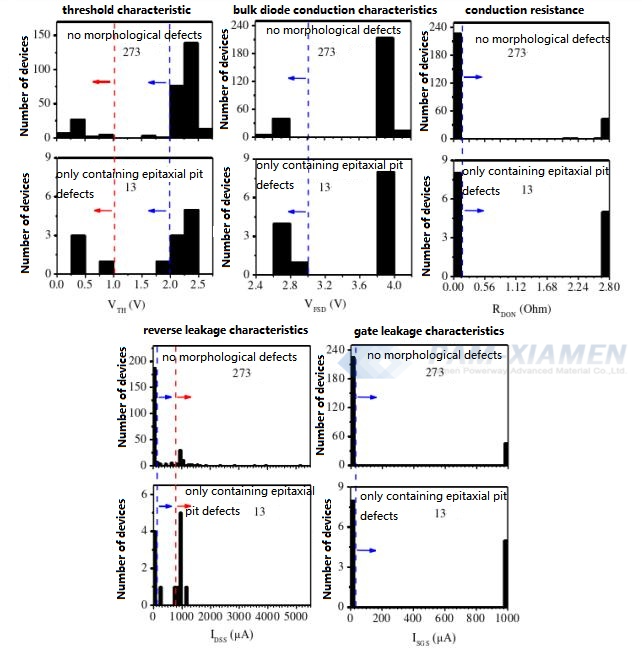

La Fig.2 mostra gli istogrammi della distribuzione statistica di cinque caratteristiche di dispositivi con difetti di fossa epitassiale. La linea tratteggiata blu rappresenta la linea di segmentazione del degrado del dispositivo, mentre la linea tratteggiata rossa rappresenta la linea di segmentazione del guasto del dispositivo. Da ciò si può vedere che il numero di dispositivi con difetti di fossa epitassiale nei campioni di MOSFET SiC è equivalente al numero di dispositivi con difetti triangolari. L'impatto dei difetti a fossa epitassiale sulle caratteristiche del dispositivo è diverso da quello dei difetti triangolari.

Fig. 2 Istogrammi di varie distribuzioni caratteristiche dei dispositivi MOSFET SiC con difetti di fossa epitassiale

In termini di guasto del dispositivo, il tasso di guasto dei dispositivi contenenti difetti di fossa epitassiale è solo del 47%. Rispetto ai difetti triangolari, l'influenza dei difetti a fossa epitassiale sulle caratteristiche di perdita inversa e sulle caratteristiche di perdita del gate del dispositivo è significativamente ridotta, con tassi di degradazione rispettivamente del 53% e del 38%, come mostrato nella tabella seguente. D'altra parte, l'influenza dei difetti dei pit epitassiali sulle caratteristiche della tensione di soglia, sulle caratteristiche di conduzione del diodo in massa e sulla resistenza di conduzione è maggiore di quella dei difetti triangolari, con tassi di degradazione che raggiungono il 38%.

| Tabella 1 Tabella statistica della correlazione tra difetti dei pit epitassiali e caratteristiche del dispositivo MOSFET SiC | |||||

|

Difetto |

VTHtasso di degrado | VFSDtasso di degrado | RASSISTENTEtasso di degrado | IDSStasso di degrado | ISGS tasso di degrado |

| Difetto della fossa epitassiale | 38% | 38% | 38% | 53% | 38% |

Nel complesso, i difetti morfologici dei pozzi epitassiali hanno un impatto significativo sul guasto e sul degrado caratteristico dei dispositivi MOSFET SiC. I dispositivi con difetti di fossa epitassiale hanno un tasso di guasto inferiore, pari al 47%. Tuttavia, l'influenza dei difetti dei pit epitassiali sulla tensione di soglia, sulle caratteristiche di conduzione del diodo in massa e sulla resistenza di conduzione del dispositivo è maggiore di quella dei difetti triangolari.

Per ulteriori informazioni potete contattarci via e-mail all'indirizzovictorchan@powerwaywafer.com e powerwaymaterial@gmail.com.