Os materiais de wafer de SiC possuem amplo bandgap, alta mobilidade de saturação de elétrons e excelentes propriedades térmicas, que apresentam grandes perspectivas de aplicação em dispositivos de alta temperatura, alta frequência e alta potência. A qualidade da superfície do Si afeta diretamente a qualidade do filme fino epitaxial de SiC e o desempenho de seus dispositivos. No entanto, defeitos na superfície C podem aumentar a densidade das luxações cristalinas, o que também pode levar à formação de defeitos na camada de crescimento da película fina epitaxial e afetar o desempenho do dispositivo. Portanto, ambas as superfícies de Si e C dos wafers de SiC exigem que suas superfícies sejam ultralisas, livres de defeitos e não danificadas.

PAM-XIAMENpode fornecer wafers SiC planos de carbono (C) processados CMP para pesquisas de preparação de dispositivos, como capacitor MOS, parâmetros específicos entre em contato com nossa equipe de vendas:victorchan@powerwaywafer.com

1.Sestudo sobre CMPTtratamentoda superfície de Sie CSseu rostoem substrato SiC

K2S2Os foram utilizados como oxidantes e nanopartículas de Al2O3 como abrasivos para comparar os efeitos de polimento CMP nas superfícies de Si e C do substrato 6H-SiC. O XPS foi utilizado para analisar o mecanismo de influência de diferentes faces do cristal nos seus efeitos de polimento CMP. Há uma diferença significativa no efeito de polimento CMP entre as superfícies Si e C das pastilhas 6H-SiC.

A taxa de remoção de material na superfície do Si atinge um valor máximo de 349 nm/h em pH=6, enquanto a taxa de remoção de material na superfície C atinge um valor máximo de 1184 nm/h em pH=2. No entanto, as faces polidas de Si e C são relativamente lisas, com valores de rugosidade Ra de 0,58 nm e 0,55 nm, respectivamente.

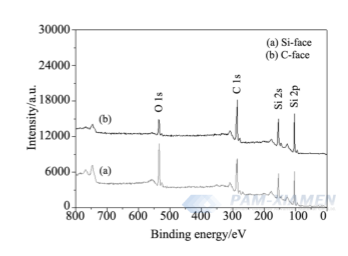

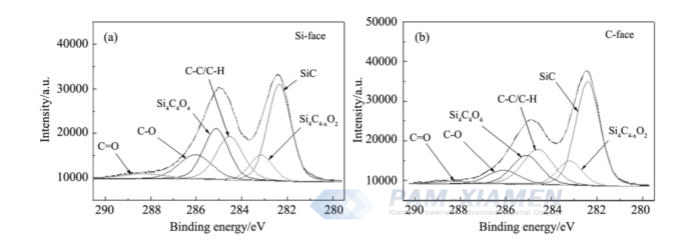

Após o polimento, os espectros XPS das superfícies de Si e C são geralmente semelhantes, mas existem diferenças significativas na composição atômica entre as superfícies de Si e C. A Figura 1 mostra que a concentração de átomos de O1s e a proporção de C/Si e O/Si na superfície de Si são maiores do que aquelas na superfície de C, mas a concentração de átomos de C1s e Si2p na superfície de C é maior do que aquela. na superfície do Si. Além disso, a relação C/Si em ambas as superfícies é superior à sua relação estequiométrica normal de 1. A intensidade de pico da energia de ligação Si-C no plano C é maior do que no plano Si, mas o conteúdo de produtos de oxidação ( como Si4-C4-x-O2, Si4-C4-O4, CO e C = O) no plano Si é maior do que no plano C, como mostrado na Fig.2. Isto indica que os óxidos no plano C são mais fáceis de remover do que no plano Si, portanto é mais fácil obter uma taxa de remoção de material mais alta no plano C do que no plano Si.

Fig. 1 Espectro XPS da superfície polida do wafer 6H-SiC

Fig. 2 Espectro C1s de superfícies polidas de 6H-SiC (a) superfície de Si; (b) Face C

2. Estudo de capacitores MOS em wafer SiC de face Si e C

Os estudiosos estudaram a correlação entre a estrutura atômica e o desempenho elétrico dos capacitores SiC MOS correspondentes e discutiram os efeitos intrínsecos e extrínsecos da estrutura da interface e dos defeitos elétricos na modulação de deslocamento de banda.

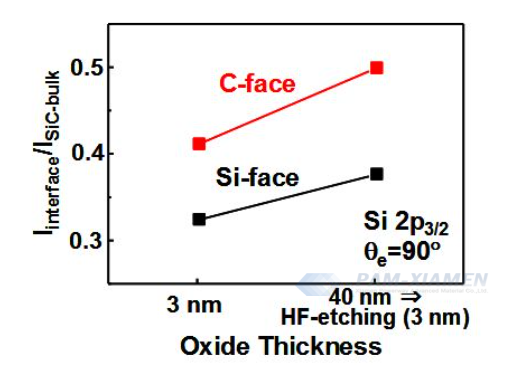

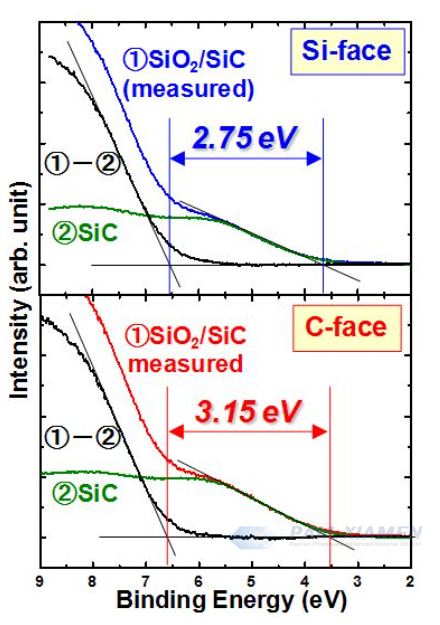

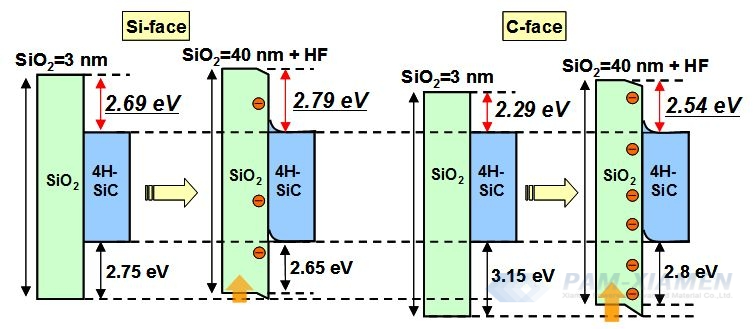

Estruturas de bandas obtidas de estruturas SiO2/SiC preparadas sob diversas condições. Os resultados indicam que o deslocamento da banda de condução que determina a corrente de fuga da porta dos dispositivos SiC MOS e a confiabilidade do óxido da porta resultante depende principalmente da orientação do substrato e da espessura do óxido. Devido ao menor deslocamento da banda de condução exibido pelo óxido fino no substrato da superfície C em comparação com o substrato da superfície Si, conclui-se que a confiabilidade reduzida dos dispositivos SiC MOS fabricados na face C é um problema inerente, que pode ser devido à diferença de eletronegatividade entre Si e os átomos de C ligados aos átomos de O na interface.

Além disso, considerando o acúmulo de cargas fixas negativas na interface SiO2/SiC, o aumento no deslocamento da banda de condução de óxidos espessos em substratos de Si e C pode ser explicado pela modulação de banda não intrínseca causada por defeitos de interface.

Do ponto de vista da redução do vazamento de porta, esse deslocamento de banda expandido de dispositivos MOS espessos é preferido, mas os defeitos elétricos devem ter um impacto negativo no desempenho e na confiabilidade do dispositivo. Portanto, estratégias básicas como a aplicação de óxidos de porta depositados e a utilização de estruturas empilhadas na engenharia de banda são essenciais para a utilização de dispositivos MOS em SiC de face C.

Fig. 3 Espectro Si 2p3/2 de mudanças na quantidade total de estados de óxido intermediários da interface de óxido cultivada em SiC (0001) Si e faces C

Fig. 4 Espectros de banda de valência de medição e deconvolução de estruturas SiO2/SiC formadas em substratos 4H-SiC com face de Si e C, indicando que o deslocamento da banda de valência de SiO2/SiC em substratos de superfície C é aproximadamente 0,4 eV maior do que na superfície de Si. .

Fig. 5 Diagrama de bandas de energia da estrutura SiO2/Si ou plano C 4H-SiC por análise síncrotron XPS. Medição do deslocamento da banda de valência na interface SiO2/SiC formada sob diversas condições.

Referências:

1. CHEN Guo-mei, NI Zi-feng,QIAN Shan-hua, LIU Yuan-xiang,DU Chun-kuan, ZHOU Ling, XU Yi-e

pt, ZHAO Yong-wu. Influência de diferentes planos cristalográficos no desempenho de CMP do wafer de SiC

2. Heiji Watanabe, Takuji Hosoi. Aspectos Fundamentais da Oxidação de Carboneto de Silício

Para mais informações, entre em contato conosco pelo e-mailvictorchan@powerwaywafer.com e powerwaymaterial@gmail.com.