Bahan wafer SiC mempunyai jurang jalur yang luas, mobiliti tepu elektron yang tinggi, dan sifat terma yang sangat baik, yang mempunyai prospek aplikasi yang hebat dalam peranti suhu tinggi, frekuensi tinggi dan berkuasa tinggi. Kualiti permukaan permukaan Si secara langsung mempengaruhi kualiti filem nipis epitaxial SiC dan prestasi perantinya. Walau bagaimanapun, kecacatan pada permukaan C boleh meningkatkan ketumpatan kehelan kristal, yang juga boleh menyebabkan pembentukan kecacatan pada lapisan pertumbuhan filem nipis epitaxial dan menjejaskan prestasi peranti. Oleh itu, kedua-dua permukaan Si dan C wafer SiC memerlukan permukaannya ultra licin, bebas kecacatan dan tidak rosak.

PAM-XIAMENboleh menyediakan wafer SiC satah Karbon (C) yang diproses CMP untuk penyelidikan penyediaan peranti, seperti kapasitor MOS, parameter khusus sila hubungi pasukan jualan kami:victorchan@powerwaywafer.com

1.Skajian tentang CMPTreatmentdaripada Si Surfacedan CSurfacepada Substrat SiC

K2S2Os digunakan sebagai oksidan dan nanopartikel Al2O3 sebagai pelelas untuk membandingkan kesan penggilap CMP pada permukaan Si dan C substrat 6H-SiC. XPS digunakan untuk menganalisis mekanisme pengaruh muka kristal yang berbeza pada kesan penggilap CMP mereka. Terdapat perbezaan yang ketara dalam kesan penggilap CMP antara permukaan Si dan C wafer 6H-SiC.

Kadar penyingkiran bahan pada permukaan Si mencapai nilai maksimum 349nm/j pada pH=6, manakala kadar penyingkiran bahan pada permukaan C mencapai nilai maksimum 1184 nm/j pada pH=2. Walau bagaimanapun, muka Si dan C yang digilap agak licin, dengan nilai kekasaran Ra 0.58nm dan 0.55nm, masing-masing.

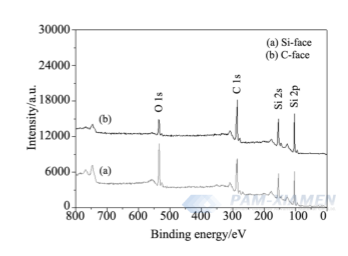

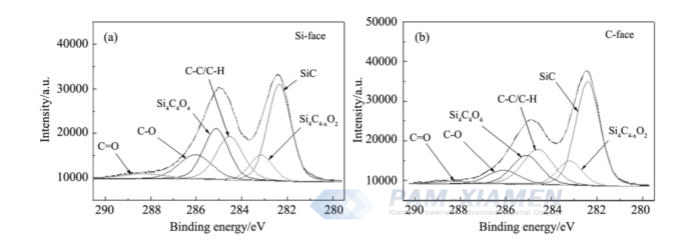

Selepas menggilap, spektrum XPS permukaan Si dan C secara amnya serupa, tetapi terdapat perbezaan ketara dalam komposisi atom antara permukaan Si dan C. Rajah 1 menunjukkan bahawa kepekatan atom O1s dan nisbah C/Si dan O/Si pada permukaan Si adalah lebih tinggi daripada pada permukaan C, tetapi kepekatan atom C1s dan Si2p pada permukaan C adalah lebih tinggi daripada itu. pada permukaan Si. Selain itu, nisbah C/Si pada kedua-dua permukaan adalah lebih tinggi daripada nisbah stoikiometri biasa mereka iaitu 1. Keamatan puncak tenaga pengikat Si-C pada satah C adalah lebih tinggi daripada pada satah Si, tetapi kandungan produk pengoksidaan ( seperti Si4-C4-x-O2, Si4-C4-O4, CO, dan C=O) pada satah Si adalah lebih tinggi daripada satah C, seperti yang ditunjukkan dalam Rajah.2. Ini menunjukkan bahawa oksida pada satah C lebih mudah dikeluarkan daripada satah Si, jadi satah C lebih mudah untuk mendapatkan kadar penyingkiran bahan yang lebih tinggi daripada pada satah Si.

Rajah 1 spektrum XPS permukaan digilap wafer 6H-SiC

Rajah 2 spektrum C1s permukaan digilap 6H-SiC (a) permukaan Si; (b) muka-C

2. Kajian Kapasitor MOS pada Si- dan C -Face SiC Wafer

Para sarjana telah mengkaji korelasi antara struktur atom dan prestasi elektrik bagi kapasitor SiC MOS yang sepadan, dan membincangkan kesan intrinsik dan ekstrinsik struktur antara muka dan kecacatan elektrik pada modulasi mengimbangi jalur.

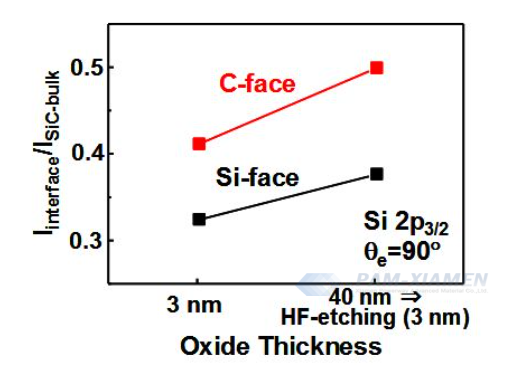

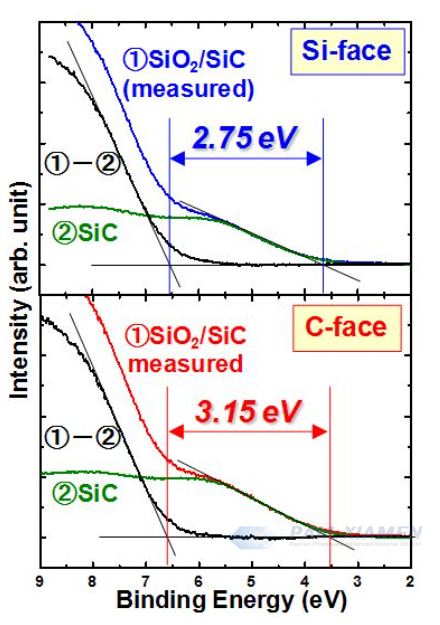

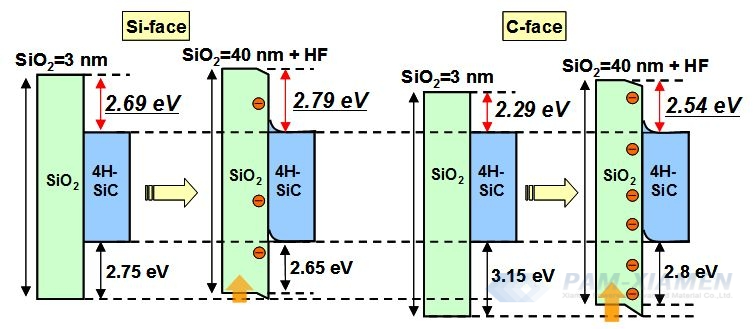

Mendapatkan struktur jalur bagi struktur SiO2/SiC yang disediakan dalam pelbagai keadaan. Keputusan menunjukkan bahawa pengimbang jalur pengaliran yang menentukan arus kebocoran pintu peranti SiC MOS dan kebolehpercayaan get oksida yang terhasil terutamanya bergantung pada orientasi substrat dan ketebalan oksida. Disebabkan oleh anjakan jalur pengaliran yang lebih kecil yang ditunjukkan oleh oksida nipis pada substrat permukaan C berbanding dengan substrat permukaan Si, ia menyimpulkan bahawa kebolehpercayaan berkurangan peranti SiC MOS yang dihasilkan pada muka C adalah isu yang wujud, yang mungkin disebabkan kepada perbezaan keelektronegatifan antara Si dan atom C yang terikat kepada atom O di antara muka.

Di samping itu, memandangkan pengumpulan caj tetap negatif pada antara muka SiO2/SiC, peningkatan dalam peralihan jalur pengaliran oksida tebal pada substrat Si dan C boleh dijelaskan oleh modulasi jalur bukan intrinsik yang disebabkan oleh kecacatan antara muka.

Daripada perspektif mengurangkan kebocoran pintu, pengimbang jalur yang diperluaskan bagi peranti MOS tebal ini lebih diutamakan, tetapi kecacatan elektrik sepatutnya memberi kesan negatif terhadap prestasi dan kebolehpercayaan peranti. Oleh itu, strategi asas seperti menggunakan oksida get terdeposit dan menggunakan struktur bertindan dalam kejuruteraan jalur adalah penting untuk menggunakan peranti MOS pada C-face SiC.

Rajah 3 Si 2p3/2 spektrum perubahan dalam jumlah keadaan oksida perantaraan daripada antara muka oksida yang ditanam pada muka SiC (0001) Si dan C

Rajah 4 Pengukuran dan penyahkonvolusian spektrum jalur valens bagi struktur SiO2/SiC yang terbentuk pada substrat 4H-SiC berhadapan Si dan C, menunjukkan bahawa anjakan jalur valens SiO2/SiC pada substrat permukaan C adalah lebih kurang 0.4 eV lebih tinggi daripada pada permukaan Si .

Rajah 5 Rajah jalur tenaga bagi struktur 4H-SiC satah SiO2/Si atau C dengan analisis synchrotron XPS. Pengukuran anjakan jalur valens pada antara muka SiO2/SiC yang terbentuk di bawah pelbagai keadaan.

Rujukan:

1. CHEN Guo-mei, NI Zi-feng,QIAN Shan-hua , LIU Yuan-xiang,DU Chun-kuan, ZHOU Ling, XU Yi-e

my, ZHAO Yong-wu. Pengaruh Satah Kristalografi Berbeza terhadap Prestasi CMP Wafer SiC

2. Heiji Watanabe, Takuji Hosoi. Aspek Asas Pengoksidaan Silikon Karbida

Untuk maklumat lanjut, sila hubungi kami e-mel divictorchan@powerwaywafer.com dan powerwaymaterial@gmail.com.