Les matériaux des plaquettes SiC ont une large bande interdite, une mobilité élevée à saturation électronique et d'excellentes propriétés thermiques, qui offrent de grandes perspectives d'application dans les dispositifs à haute température, haute fréquence et haute puissance. La qualité de la surface de Si affecte directement la qualité du film mince épitaxial de SiC et les performances de ses dispositifs. Cependant, les défauts sur la surface C peuvent augmenter la densité des dislocations cristallines, ce qui peut également conduire à la formation de défauts dans la couche de croissance du film mince épitaxial et affecter les performances du dispositif. Par conséquent, les surfaces Si et C des plaquettes SiC nécessitent que leurs surfaces soient ultra lisses, exemptes de défauts et intactes.

PAM-XIAMENpeut fournir des plaquettes SiC planes en carbone (C) traitées par CMP pour les recherches sur la préparation de dispositifs, comme le condensateur MOS, paramètres spécifiques, veuillez contacter notre équipe commerciale :victorchan@powerwaywafer.com

1.Sétude sur le CMPTtraitementde Si SurfaceetCSta têtesur substrat SiC

Les K2S2O ont été utilisés comme oxydants et les nanoparticules d'Al2O3 comme abrasifs pour comparer les effets de polissage du CMP sur les surfaces Si et C du substrat 6H-SiC. XPS a été utilisé pour analyser le mécanisme d'influence de différentes faces cristallines sur leurs effets de polissage CMP. Il existe une différence significative dans l'effet de polissage CMP entre les surfaces Si et C des plaquettes 6H-SiC.

Le taux d'enlèvement de matière sur la surface Si atteint une valeur maximale de 349 nm/h à pH=6, tandis que le taux d'enlèvement de matière sur la surface C atteint une valeur maximale de 1184 nm/h à pH=2. Cependant, les faces polies en Si et C sont relativement lisses, avec des valeurs de rugosité Ra de 0,58 nm et 0,55 nm, respectivement.

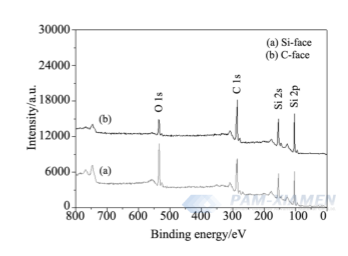

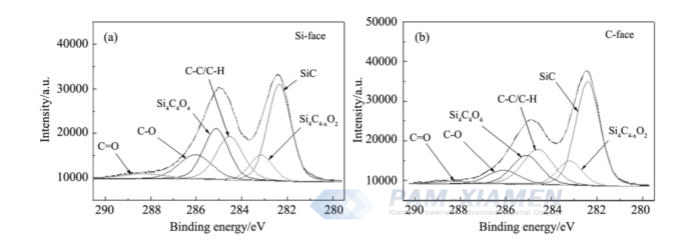

Après polissage, les spectres XPS des surfaces Si et C sont généralement similaires, mais il existe des différences significatives dans la composition atomique entre les surfaces Si et C. La figure 1 montre que la concentration d'atomes O1s et le rapport C/Si et O/Si sur la surface Si sont supérieurs à ceux de la surface C, mais que la concentration d'atomes C1s et Si2p sur la surface C est supérieure à celle-ci. sur la surface du Si. De plus, le rapport C/Si sur les deux surfaces est supérieur à leur rapport stoechiométrique normal de 1. L'intensité maximale de l'énergie de liaison Si-C sur le plan C est supérieure à celle sur le plan Si, mais la teneur en produits d'oxydation ( tels que Si4-C4-x-O2, Si4-C4-O4, CO et C=O) sur le plan Si est supérieur à celui sur le plan C, comme le montre la figure 2. Cela indique que les oxydes sur le plan C sont plus faciles à éliminer que sur le plan Si, de sorte que le plan C est plus facile à obtenir un taux d'élimination de matière plus élevé que sur le plan Si.

Fig. 1 Spectre XPS de la surface polie d'une plaquette de 6H-SiC

Fig. 2 Spectre C1s de surfaces polies de 6H-SiC (a) surface Si ; (b) Face C

2. Etude des condensateurs MOS sur plaquette SiC Si- et C-Face

Les chercheurs ont étudié la corrélation entre la structure atomique et les performances électriques des condensateurs SiC MOS correspondants, et ont discuté des effets intrinsèques et extrinsèques de la structure de l'interface et des défauts électriques sur la modulation de décalage de bande.

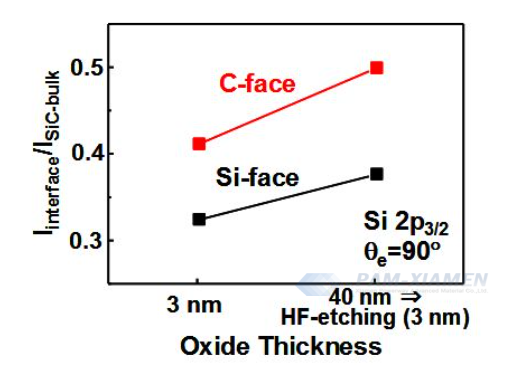

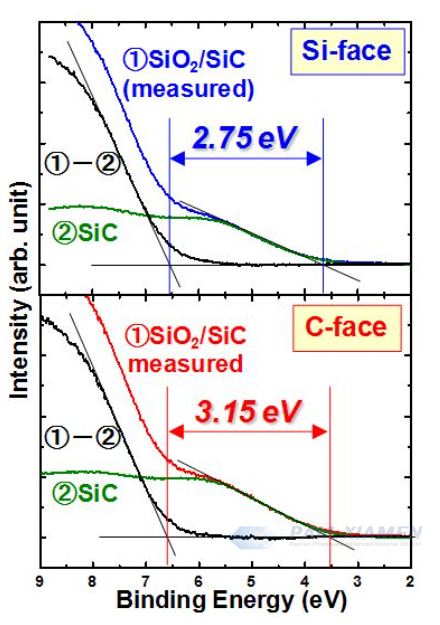

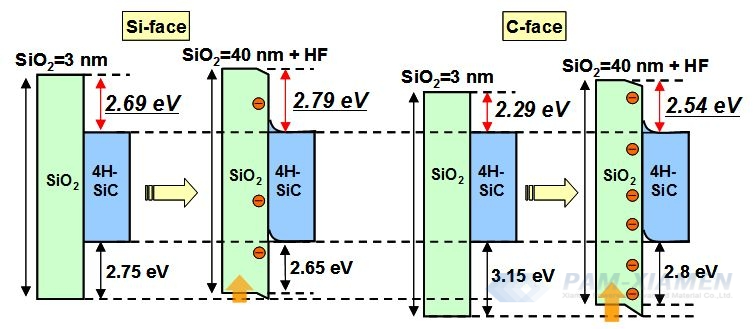

Structures de bandes obtenues de structures SiO2/SiC préparées dans diverses conditions. Les résultats indiquent que le décalage de bande de conduction qui détermine le courant de fuite de grille des dispositifs SiC MOS et la fiabilité de l'oxyde de grille qui en résulte dépendent principalement de l'orientation du substrat et de l'épaisseur de l'oxyde. En raison du plus petit décalage de bande de conduction présenté par l'oxyde mince sur le substrat de surface C par rapport au substrat de surface en Si, il conclut que la fiabilité réduite des dispositifs SiC MOS fabriqués sur la face C est un problème inhérent, qui peut être dû à la différence d'électronégativité entre Si et les atomes de C liés aux atomes d'O à l'interface.

De plus, compte tenu de l’accumulation de charges fixes négatives à l’interface SiO2/SiC, l’augmentation du décalage de bande de conduction des oxydes épais sur les substrats Si et C peut s’expliquer par la modulation de bande non intrinsèque provoquée par les défauts d’interface.

Du point de vue de la réduction des fuites de grille, ce décalage de bande élargi des dispositifs MOS épais est préféré, mais les défauts électriques devraient avoir un impact négatif sur les performances et la fiabilité du dispositif. Par conséquent, des stratégies de base telles que l’application d’oxydes de grille déposés et l’utilisation de structures empilées dans l’ingénierie des bandes sont essentielles pour l’utilisation de dispositifs MOS sur SiC à face C.

Fig. 3 Spectre Si 2p3/2 de changements dans la quantité totale d'états d'oxyde intermédiaires à partir de l'interface d'oxyde cultivée sur SiC (0001) faces Si et C

Fig. 4 Spectres de bande de valence de mesure et de déconvolution des structures SiO2/SiC formées sur des substrats 4H-SiC à face Si et C, indiquant que le décalage de bande de valence de SiO2/SiC sur des substrats à surface C est environ 0,4 eV supérieur à celui de la surface Si. .

Fig. 5 Diagramme de bande d'énergie de la structure SiO2/Si ou 4H-SiC plan C par analyse XPS synchrotron. Mesure du décalage de bande de valence à l'interface SiO2/SiC formée dans diverses conditions.

Les références:

1. CHEN Guo-mei, NI Zi-feng, QIAN Shan-hua, LIU Yuan-xiang, DU Chun-kuan, ZHOU Ling, XU Yi-e

fr, ZHAO Yong-wu. Influence de différents plans cristallographiques sur les performances CMP de la plaquette SiC

2. Heiji Watanabe, Takuji Hosoi. Aspects fondamentaux de l'oxydation du carbure de silicium

Pour plus d'informations, veuillez nous contacter par email àvictorchan@powerwaywafer.cometpowerwaymaterial@gmail.com.