I materiali per wafer SiC hanno un ampio gap di banda, un'elevata mobilità di saturazione elettronica ed eccellenti proprietà termiche, che hanno grandi prospettive di applicazione in dispositivi ad alta temperatura, alta frequenza e alta potenza. La qualità della superficie del Si influenza direttamente la qualità del film sottile epitassiale SiC e le prestazioni dei suoi dispositivi. Tuttavia, i difetti sulla superficie C possono aumentare la densità delle dislocazioni dei cristalli, che possono anche portare alla formazione di difetti nello strato di crescita del film sottile epitassiale e influenzare le prestazioni del dispositivo. Pertanto, sia le superfici Si che C dei wafer SiC richiedono che le loro superfici siano ultra lisce, prive di difetti e non danneggiate.

PAM-XIAMENpuò fornire wafer SiC piani in carbonio (C) elaborati CMP per ricerche sulla preparazione dei dispositivi, come condensatori MOS, parametri specifici si prega di contattare il nostro team di vendita:victorchan@powerwaywafer.com

1.Sstudio sul CMPTtrattamentodella superficie Sie CSla tua facciasul substrato SiC

I K2S2O sono stati utilizzati come ossidanti e le nanoparticelle Al2O3 come abrasivi per confrontare gli effetti di lucidatura del CMP sulle superfici Si e C del substrato 6H-SiC. XPS è stato utilizzato per analizzare il meccanismo di influenza delle diverse facce dei cristalli sui loro effetti di lucidatura CMP. Esiste una differenza significativa nell'effetto di lucidatura CMP tra le superfici Si e C dei wafer 6H-SiC.

La velocità di rimozione del materiale sulla superficie del Si raggiunge un valore massimo di 349 nm/h a pH=6, mentre la velocità della rimozione del materiale sulla superficie di C raggiunge un valore massimo di 1184 nm/h a pH=2. Tuttavia, le facce lucide di Si e C sono relativamente lisce, con valori di rugosità Ra rispettivamente di 0,58 nm e 0,55 nm.

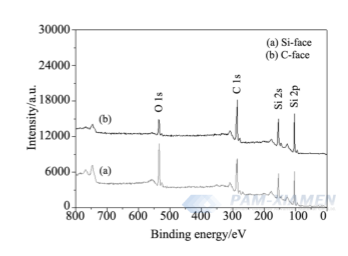

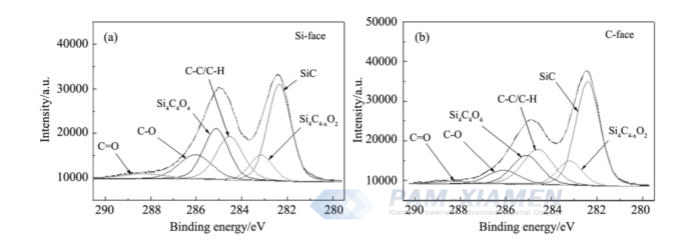

Dopo la lucidatura, gli spettri XPS delle superfici Si e C sono generalmente simili, ma esistono differenze significative nella composizione atomica tra le superfici Si e C. La Fig. 1 mostra che la concentrazione di atomi di O1s e il rapporto di C/Si e O/Si sulla superficie del Si sono superiori a quelli sulla superficie del C, ma la concentrazione degli atomi di C1s e Si2p sulla superficie del C è superiore a quella sulla superficie del Si. Inoltre, il rapporto C/Si su entrambe le superfici è superiore al normale rapporto stechiometrico pari a 1. L'intensità di picco dell'energia di legame Si-C sul piano C è superiore a quella sul piano Si, ma il contenuto di prodotti di ossidazione ( come Si4-C4-x-O2, Si4-C4-O4, CO e C=O) sul piano Si è maggiore di quello sul piano C, come mostrato in Fig.2. Ciò indica che gli ossidi sul piano C sono più facili da rimuovere rispetto al piano Si, quindi è più facile ottenere un tasso di rimozione del materiale più elevato sul piano C rispetto al piano Si.

Fig. 1 Spettro XPS della superficie lucida del wafer 6H-SiC

Fig. 2 Spettro C1s delle superfici lucide di 6H-SiC (a) Superficie Si; (b) Faccia C

2. Studio di condensatori MOS su wafer SiC Si- e C -Face

Gli studiosi hanno studiato la correlazione tra la struttura atomica e le prestazioni elettriche dei corrispondenti condensatori MOS SiC e hanno discusso gli effetti intrinseci ed estrinseci della struttura dell'interfaccia e dei difetti elettrici sulla modulazione dell'offset di banda.

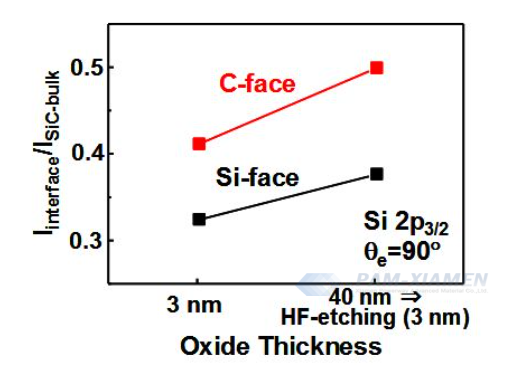

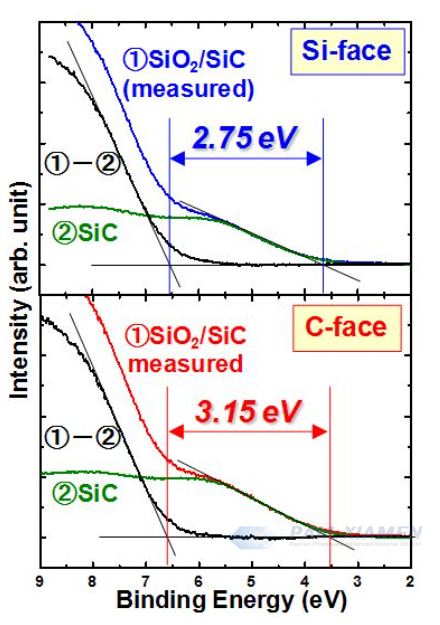

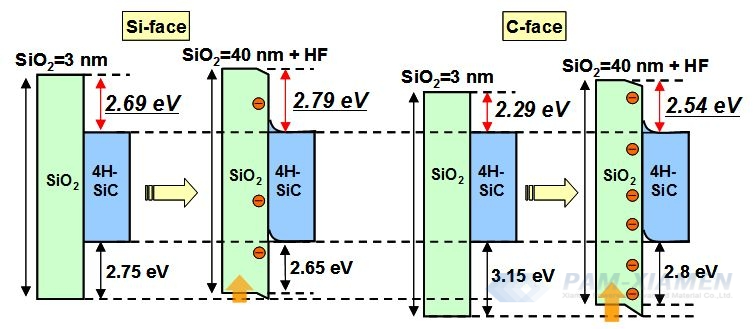

Obtained band structures of SiO2/SiC structures prepared under various conditions. The results indicate that the conduction band offset that determines the gate leakage current of SiC MOS devices and the resulting gate oxide reliability mainly depends on the substrate orientation and oxide thickness. Due to the smaller conduction band shift exhibited by the thin oxide on the C-surface substrate compared to the Si surface substrate, it concludes that the reduced reliability of SiC MOS devices manufactured on the C-face is an inherent issue, which may be due to the difference in electronegativity between Si and the C atoms bound to O atoms at the interface.

In addition, considering the accumulation of negative fixed charges at the SiO2/SiC interface, the increase in conduction band shift of thick oxides on Si and C substrates can be explained by the non intrinsic band modulation caused by interface defects.

From the perspective of reducing gate leakage, this expanded band offset of thick MOS devices is preferred, but electrical defects should have a negative impact on device performance and reliability. Therefore, basic strategies such as applying deposited gate oxides and utilizing stacked structures in band engineering are essential for utilizing MOS devices on C-face SiC.

Fig. 3 Spettro Si 2p3/2 dei cambiamenti nella quantità totale di stati di ossido intermedi dall'interfaccia di ossido cresciuta su facce Si e C di SiC (0001)

Fig. 4 Misurazione e spettri della banda di valenza di deconvoluzione delle strutture SiO2/SiC formate su substrati 4H-SiC con facce di Si e C, che indicano che lo spostamento della banda di valenza di SiO2/SiC sui substrati con superficie C è di circa 0,4 eV superiore a quello sulla superficie di Si .

Fig. 5 Diagramma delle bande energetiche della struttura 4H-SiC del piano SiO2/Si o C mediante analisi XPS al sincrotrone. Misurazione dello spostamento della banda di valenza all'interfaccia SiO2/SiC formata in varie condizioni.

Riferimenti:

1. CHEN Guo-mei, NI Zi-feng,QIAN Shan-hua, LIU Yuan-xiang,DU Chun-kuan, ZHOU Ling, XU Yi-e

it, ZHAO Yong-wu. Influenza di diversi piani cristallografici sulle prestazioni CMP del wafer SiC

2. Heiji Watanabe, Takuji Hosoi. Aspetti fondamentali dell'ossidazione del carburo di silicio

Per ulteriori informazioni potete contattarci via e-mail all'indirizzovictorchan@powerwaywafer.com e powerwaymaterial@gmail.com.