SiC 웨이퍼 재료는 넓은 밴드갭, 높은 전자 포화 이동도 및 우수한 열 특성을 갖고 있어 고온, 고주파 및 고전력 장치에 응용 가능성이 높습니다. Si 표면의 표면 품질은 SiC 에피택셜 박막의 품질과 장치 성능에 직접적인 영향을 미칩니다. 그러나 C 표면의 결함은 결정 전위의 밀도를 증가시킬 수 있으며, 이는 또한 에피택시 박막 성장층의 결함 형성으로 이어져 소자 성능에 영향을 줄 수도 있습니다. 따라서 SiC 웨이퍼의 Si 및 C 표면은 표면이 매우 매끄럽고 결함이 없으며 손상되지 않아야 합니다.

PAM-하문MOS 커패시터와 같은 장치 준비 연구를 위해 CMP 처리된 탄소(C) 평면 SiC 웨이퍼를 제공할 수 있습니다. 특정 매개변수는 당사 영업팀에 문의하십시오.victorchan@powerwaywafer.com

1.SCMP에 대한 연구T치료Si 표면의과 CS표면SiC 기판에

6H-SiC 기판의 Si 및 C 표면에 대한 CMP 연마 효과를 비교하기 위해 K2S2O를 산화제로 사용하고 Al2O3 나노 입자를 연마제로 사용했습니다. XPS는 CMP 연마 효과에 대한 다양한 결정면의 영향 메커니즘을 분석하는 데 사용되었습니다. 6H-SiC 웨이퍼의 Si와 C 표면 사이의 CMP 연마 효과에는 상당한 차이가 있습니다.

Si 표면의 물질 제거 속도는 pH=6에서 최대값 349nm/h에 도달하는 반면, C 표면의 물질 제거 속도는 pH=2에서 최대값 1184nm/h에 도달합니다. 그러나 연마된 Si 및 C 면은 상대적으로 매끄러우며 거칠기 값 Ra는 각각 0.58nm 및 0.55nm입니다.

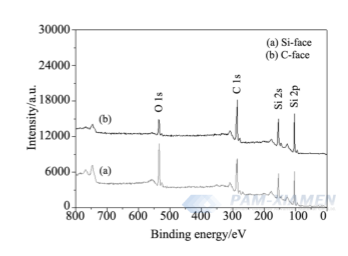

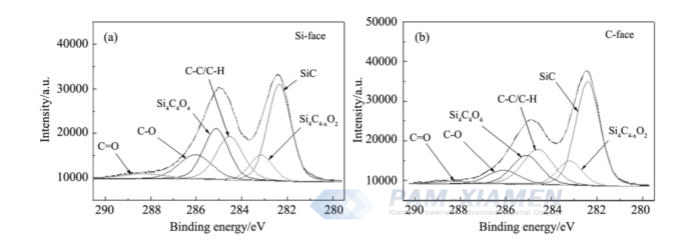

연마 후 Si와 C 표면의 XPS 스펙트럼은 일반적으로 유사하지만 Si와 C 표면 사이의 원자 구성에는 상당한 차이가 있습니다. 그림 1은 Si 표면의 O1s 원자 농도와 C/Si 및 O/Si 비율이 C 표면보다 높지만 C 표면의 C1s 및 Si2p 원자 농도가 그보다 높음을 보여줍니다. Si 표면에. 더욱이, 양쪽 표면의 C/Si 비율은 일반적인 화학량론적 비율인 1보다 높습니다. C 평면의 Si-C 결합 에너지의 피크 강도는 Si 평면의 피크 강도보다 높지만 산화 생성물의 함량( 그림 2에 표시된 것처럼 Si 평면의 Si4-C4-x-O2, Si4-C4-O4, CO 및 C=O)는 C 평면의 것보다 높습니다. 이는 C 평면의 산화물이 Si 평면보다 제거하기 쉽기 때문에 C 평면이 Si 평면보다 더 높은 재료 제거율을 얻기가 더 쉽다는 것을 나타냅니다.

그림 1. 6H-SiC 웨이퍼 연마 표면의 XPS 스펙트럼

그림 2 6H-SiC의 연마된 표면의 C1s 스펙트럼 (a) Si 표면; (b) C면

2. Si- 및 C-Face SiC 웨이퍼의 MOS 커패시터 연구

학자들은 해당 SiC MOS 커패시터의 원자 구조와 전기적 성능 간의 상관 관계를 연구하고 인터페이스 구조의 내재적 및 외적 효과와 밴드 오프셋 변조에 대한 전기적 결함에 대해 논의했습니다.

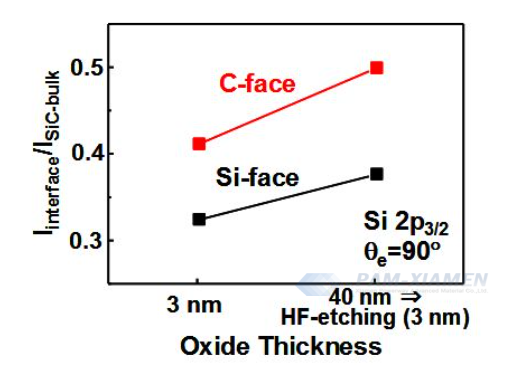

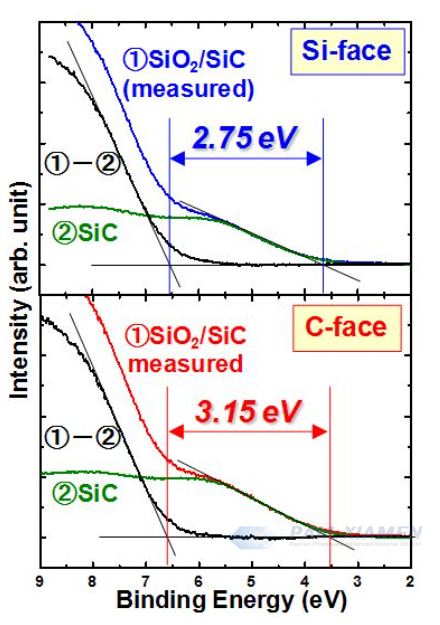

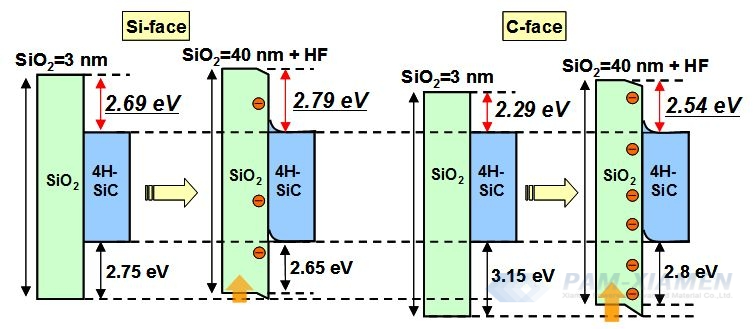

다양한 조건에서 제조된 SiO2/SiC 구조의 밴드 구조를 얻었습니다. 결과는 SiC MOS 장치의 게이트 누설 전류를 결정하는 전도대 오프셋과 그에 따른 게이트 산화물 신뢰성이 주로 기판 방향과 산화물 두께에 따라 달라진다는 것을 나타냅니다. Si 표면 기판에 비해 C 표면 기판의 얇은 산화물에 의해 나타나는 전도대 이동이 더 작기 때문에 C 표면에서 제조된 SiC MOS 장치의 신뢰성 감소가 본질적인 문제라고 결론지었습니다. Si와 계면에서 O 원자에 결합된 C 원자 사이의 전기 음성도 차이.

또한, SiO2/SiC 인터페이스에서 음의 고정 전하 축적을 고려하면 Si 및 C 기판의 두꺼운 산화물의 전도대 이동 증가는 인터페이스 결함으로 인한 비내재적 밴드 변조로 설명될 수 있습니다.

게이트 누출을 줄이는 관점에서 볼 때 두꺼운 MOS 장치의 대역 오프셋 확장이 선호되지만 전기적 결함은 장치 성능과 신뢰성에 부정적인 영향을 미칩니다. 따라서 C-face SiC에서 MOS 소자를 활용하기 위해서는 증착된 게이트 산화물을 적용하고 밴드 엔지니어링에서 적층 구조를 활용하는 등의 기본 전략이 필수적입니다.

그림 3 SiC(0001) Si 및 C 면에서 성장한 산화물 계면의 중간 산화물 상태 총량 변화에 대한 Si 2p3/2 스펙트럼

그림 4. Si 및 C 표면 4H-SiC 기판에 형성된 SiO2/SiC 구조의 측정 및 디콘볼루션 가전자대 스펙트럼. 이는 C 표면 기판의 SiO2/SiC 가전자대 이동이 Si 표면의 가전자대 이동보다 약 0.4eV 더 높다는 것을 나타냅니다. .

그림 5 싱크로트론 XPS 분석에 의한 SiO2/Si 또는 C 평면 4H-SiC 구조의 에너지 밴드 다이어그램. 다양한 조건에서 형성된 SiO2/SiC 계면의 가전자대 이동 측정.

참고문헌:

1. CHEN Guo-mei, NI Zi-feng,QIAN Shan-hua, LIU Yuan-xiang,DU Chun-kuan, ZHOU Ling, XU Yi-e

엥, 자오용우. SiC 웨이퍼의 CMP 성능에 대한 다양한 결정학적 평면의 영향

2. 와타나베 헤이지, 호소이 타쿠지. 탄화규소 산화의 기본 측면

자세한 내용은 이메일로 문의해 주세요.victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.