SiC-Wafermaterialien verfügen über eine große Bandlücke, eine hohe Elektronensättigungsmobilität und ausgezeichnete thermische Eigenschaften, die große Anwendungsaussichten in Hochtemperatur-, Hochfrequenz- und Hochleistungsgeräten bieten. Die Oberflächenqualität der Si-Oberfläche wirkt sich direkt auf die Qualität der epitaktischen SiC-Dünnschicht und die Leistung ihrer Geräte aus. Defekte auf der C-Oberfläche können jedoch die Dichte von Kristallversetzungen erhöhen, was auch zur Bildung von Defekten in der Wachstumsschicht des epitaktischen Dünnfilms führen und die Geräteleistung beeinträchtigen kann. Daher müssen sowohl die Si- als auch die C-Oberfläche von SiC-Wafern extrem glatt, fehlerfrei und unbeschädigt sein.

PAM-XIAMENkann CMP-verarbeitete Kohlenstoff-(C)-Ebenen-SiC-Wafer für Gerätevorbereitungsforschungen bereitstellen, wie z. B. MOS-Kondensatoren. Spezifische Parameter kontaktieren Sie bitte unser Vertriebsteam:victorchan@powerwaywafer.com

1.SStudie zu CMPTBehandlungder Si-Oberflächeund CSDein Gesichtauf SiC-Substrat

K2S2Os wurden als Oxidationsmittel und Al2O3-Nanopartikel als Schleifmittel verwendet, um die CMP-Poliereffekte auf den Si- und C-Oberflächen des 6H-SiC-Substrats zu vergleichen. XPS wurde verwendet, um den Einflussmechanismus verschiedener Kristallflächen auf ihre CMP-Poliereffekte zu analysieren. Es gibt einen signifikanten Unterschied in der CMP-Polierwirkung zwischen den Si- und C-Oberflächen von 6H-SiC-Wafern.

Die Materialabtragsrate auf der Si-Oberfläche erreicht einen Maximalwert von 349 nm/h bei pH=6, während die Materialabtragsrate auf der C-Oberfläche einen Maximalwert von 1184 nm/h bei pH=2 erreicht. Allerdings sind die polierten Si- und C-Flächen relativ glatt, mit Rauheitswerten Ra von 0,58 nm bzw. 0,55 nm.

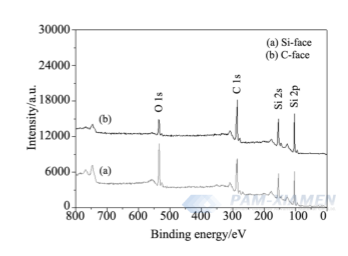

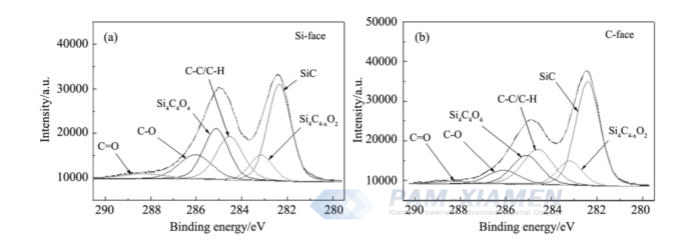

Nach dem Polieren sind die XPS-Spektren der Si- und C-Oberflächen im Allgemeinen ähnlich, es gibt jedoch erhebliche Unterschiede in der atomaren Zusammensetzung zwischen den Si- und C-Oberflächen. Abb. 1 zeigt, dass die Konzentration der O1s-Atome und das Verhältnis von C/Si und O/Si auf der Si-Oberfläche höher sind als auf der C-Oberfläche, aber die Konzentration der C1s- und Si2p-Atome auf der C-Oberfläche ist höher auf der Si-Oberfläche. Darüber hinaus ist das C/Si-Verhältnis auf beiden Oberflächen höher als ihr normales stöchiometrisches Verhältnis von 1. Die Spitzenintensität der Si-C-Bindungsenergie auf der C-Ebene ist höher als die auf der Si-Ebene, aber der Gehalt an Oxidationsprodukten ( (z. B. Si4-C4-x-O2, Si4-C4-O4, CO und C=O) auf der Si-Ebene höher ist als auf der C-Ebene, wie in Abb. 2 dargestellt. Dies weist darauf hin, dass die Oxide auf der C-Ebene leichter zu entfernen sind als auf der Si-Ebene, sodass auf der C-Ebene leichter eine höhere Materialabtragsrate als auf der Si-Ebene erzielt werden kann.

Abb. 1 XPS-Spektrum der polierten Oberfläche eines 6H-SiC-Wafers

Abb. 2 C1s-Spektrum polierter Oberflächen von 6H-SiC (a) Si-Oberfläche; (b) C-Fläche

2. Untersuchung von MOS-Kondensatoren auf Si- und C-Face-SiC-Wafern

Wissenschaftler haben den Zusammenhang zwischen der Atomstruktur und der elektrischen Leistung entsprechender SiC-MOS-Kondensatoren untersucht und die intrinsischen und extrinsischen Auswirkungen der Grenzflächenstruktur und elektrischer Defekte auf die Bandoffsetmodulation diskutiert.

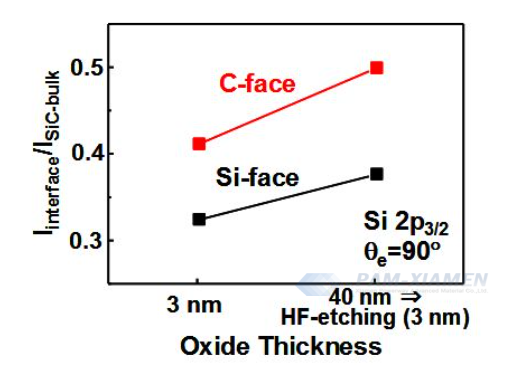

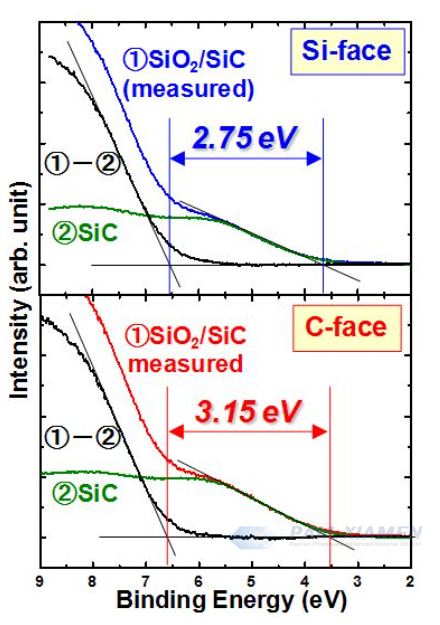

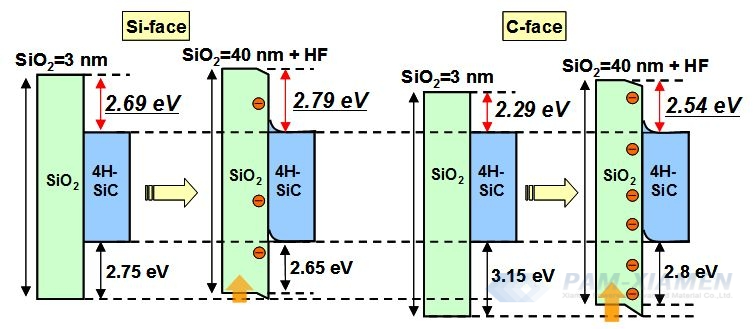

Erhaltene Bandstrukturen von SiO2/SiC-Strukturen, hergestellt unter verschiedenen Bedingungen. Die Ergebnisse zeigen, dass der Leitungsbandversatz, der den Gate-Leckstrom von SiC-MOS-Bauelementen und die daraus resultierende Gate-Oxid-Zuverlässigkeit bestimmt, hauptsächlich von der Substratausrichtung und der Oxiddicke abhängt. Aufgrund der geringeren Leitungsbandverschiebung, die das dünne Oxid auf dem C-Oberflächensubstrat im Vergleich zum Si-Oberflächensubstrat aufweist, wird der Schluss gezogen, dass die verringerte Zuverlässigkeit von SiC-MOS-Bauelementen, die auf der C-Oberfläche hergestellt werden, ein inhärentes Problem darstellt, das darauf zurückzuführen sein könnte auf den Unterschied in der Elektronegativität zwischen Si und den C-Atomen, die an der Grenzfläche an O-Atome gebunden sind.

Wenn man außerdem die Anhäufung negativer Festladungen an der SiO2/SiC-Grenzfläche berücksichtigt, kann die Zunahme der Leitungsbandverschiebung von dicken Oxiden auf Si- und C-Substraten durch die durch Grenzflächendefekte verursachte nicht-intrinsische Bandmodulation erklärt werden.

Im Hinblick auf die Reduzierung des Gate-Leckstroms wird dieser erweiterte Bandversatz dicker MOS-Geräte bevorzugt, elektrische Defekte sollten sich jedoch negativ auf die Leistung und Zuverlässigkeit der Geräte auswirken. Daher sind grundlegende Strategien wie das Aufbringen abgeschiedener Gate-Oxide und die Verwendung gestapelter Strukturen in der Bandtechnik für die Verwendung von MOS-Bauelementen auf C-Face-SiC unerlässlich.

Abb. 3 Si 2p3/2-Spektrum der Änderungen in der Gesamtmenge der Zwischenoxidzustände von der Oxidgrenzfläche, die auf SiC-(0001)-Si- und C-Flächen gewachsen ist

Abb. 4 Messung und Entfaltung der Valenzbandspektren von SiO2/SiC-Strukturen, die auf Si- und C-beschichteten 4H-SiC-Substraten gebildet wurden. Dies zeigt, dass die Valenzbandverschiebung von SiO2/SiC auf Substraten mit C-Oberfläche etwa 0,4 eV höher ist als auf der Si-Oberfläche .

Abb. 5 Energiebanddiagramm der SiO2/Si- oder C-Ebenen-4H-SiC-Struktur durch Synchrotron-XPS-Analyse. Messung der Valenzbandverschiebung an der unter verschiedenen Bedingungen gebildeten SiO2/SiC-Grenzfläche.

Verweise:

1. CHEN Guo-mei, NI Zi-feng, QIAN Shan-hua, LIU Yuan-xiang, DU Chun-kuan, ZHOU Ling, XU Yi-e

de, ZHAO Yong-wu. Einfluss verschiedener kristallographischer Ebenen auf die CMP-Leistung von SiC-Wafern

2. Heiji Watanabe, Takuji Hosoi. Grundlegende Aspekte der Siliziumkarbidoxidation

Für weitere Informationen kontaktieren Sie uns bitte per E-Mail untervictorchan@powerwaywafer.com und powerwaymaterial@gmail.com.