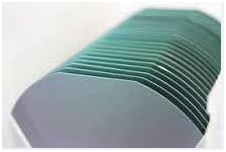

L'épitaxie de silicium avec dopant au bore de taille 200 mm de PAM-XIAMEN est disponible pour la fabrication de dispositifs semi-conducteurs. La croissance par épitaxie du silicium est un processus de traitement de surface pour les plaquettes de silicium, ce qui signifie qu'un film monocristallin est superposé sur la plaquette polie par réaction chimique ou par d'autres moyens, et la couche de film est la couche épitaxiale de silicium. Pour en savoir plus sur l'épitaxie à base de silicium de 200 mm, veuillez vous référer au tableau répertorié.

1. Paramètres de la plaquette épitaxiale de silicium

PAM210531-SIEPI

| Plaquette de silicium épitaxiale de 200 mm | |||||

| élément | Unités | Limites | Méthode D'essai | Commentaires | |

| 1 Caractéristiques du cristal/en vrac | |||||

| 1.1 | Procédé de croissance | – | – | – | CZ |

| 1.2 | Orientation | – | (100) | – | – |

| 1.3 | dopant | – | Bore | – | – |

| 1.4 | Résistivité | Ohm*cm | 0.01-0.02 | – | – |

| 1.5 | Variation de résistivité radiale | % | 10 % maximum | ASTM F81 plan B | |

| 1.6 | Concentration d'oxygène | ppma | 10-16 | Nouvelle norme ASTM (F121-83) K=2,45 | |

| 1.7 | Variation radiale de l'oxygène | % | ≤10% | – | – |

| 1.8 | Concentration de métaux en vrac, Fe | À/cm3 | NA | – | Cu/Fe/Ni/Al/Zn |

| 1.9 | Concentration de carbone | À/cm3 | Max 2.0*1016 | – | – |

| 1.10 | Luxations | – | Aucun | – | Après gravure |

| 1.11 | Glissement, lignée, jumeaux, tourbillon, fosses peu profondes | – | – | ||

| 2 plaquette/substrat poli | |||||

| 2.1 | Orientation de la surface | Degré | (100)±0,5 | – | – |

| 2.2 | Diamètre | mm | 200±0,2 | – | – |

| 2.3 | Épaisseur | mm | 725±20 | – | – |

| 2.4 | Plat Longueur primaire | mm | entaillée | – | SEMI M1.9-0699 |

| 2.5 | Orientation Plat principal | Degré | {100} | – | – |

| 2.6 | Bord Profi (angle) | – | SEMI | – | – |

| 2.7 | Caractéristiques d'inspection visuelle de la surface avant spécifiées selon SEMI M1-0200 Tableau 1 | ||||

| 2.8 | Surface arrière

Poly+ LTO(SiO2) |

Poly

8000±800+LTO8000±800A LTO extérieur |

– | – | |

| 2.9 | Exclusion périphérique (LTO)

-face arrière -face avant |

mm | 0.5~2.0

Aucun |

– | – |

| 2.10 | Caractéristiques d'inspection visuelle de la surface arrière spécifiées selon SEMI M1-0200 Tableau 1 | ||||

| 3Patte/Couche épitaxiale | |||||

| 3.1 | Métaux de surface | À/cm-2 | 5E10 | – | Cu/Fe/Ni/Al/Zn |

| 3.2 | Bow / chaîne | um | ≤50 | – | – |

| 3.3 | Variation d'épaisseur totale (TTV) | um | ≤4 | – | – |

| 3.4 | Planéité du site (SFQR) | um | ≤1 | – | 20*20mm, 100%

PUA |

| 3.5 | dopant | – | Bore | – | – |

| 3.6 | Plage cible d'épaisseur | mm | Selon le code épi pour la pièce jointe | ||

| 3.7 | Tolérance d'épaisseur, w/w | % | <5 | Centre (1 pt) 10 mm du bord (4 pts @ 90 degrés)

[Tmax-Tmin]÷[Tmax+Tmin]*100% |

|

| 3.8 | Plage de résistivité | Ohm*cm | Selon le code épi pour la pièce jointe | ||

| 3.9 | Tolérance de résistivité, w/w | % | <5 | Centre (1 pt) 10 mm du bord (4 pts @ 90 degrés)

[Rmax-Rmin]÷[Rmax+Rmin]*100% |

|

| 3.10 | Couronne de bord | – | NA | La projection au-dessus de la surface de la plaquette ne doit pas dépasser 1/3 de l'épaisseur de la couche épi | |

| 3.11 | Défauts d'empilement | cm-2 | ≤0.1 | ASTM F1810 | – |

| 3.12 | Etch Densité Pit | cm-2 | ≤5 | – | – |

| 3.13 | Ligne de glissement | – | SEMI M2-0997 | ASTM F523, SEMI M17 | – |

| 3.14 | Égratignures, fossettes, écorces d'orange,

Fissures/fractures, pattes d'oie, brume, Matières étrangères |

– | Aucun | ASTMF523 | – |

| 3.15 | Jetons de bord | – | Aucun | ASTMF523 | |

| 3.16 | Défaut du point lumineux (saillie, intrusion,

pic, etc.) |

EA

um |

Aucun | ASTMF523 | Inspection de surface automatique au laser |

| 3.17 | Exclusion d'arête nominale | mm | 3 | Pour les articles 3.2~3.4, 3.11~3.14, 3.16 | |

| Caractéristiques d'inspection visuelle de la surface avant spécifiées selon SEMI Tableau 5 SEMI M11-0200 | |||||

| 4.1 | Marquage laser au dos dur, opposé à l'encoche, SEMI M12 | ||||

| Caractéristiques d'inspection visuelle de la surface arrière spécifiées selon SEMI Tableau 5 SEMI M11-0200 | |||||

Attachment for Technical Specification Epi

| Gamme de résistivité Ohm*cm | Gamme d'épaisseur mm | ||

| 1 | MM6Bp 12.0_15.0 | 12±10% | 15±5% |

2. Processus d'épitaxie du silicium

La technologie d'épitaxie dans le silicium a été développée dans les années 1960 et s'est principalement développée en trois méthodes : l'épitaxie en phase gazeuse, l'épitaxie en phase liquide et l'épitaxie par faisceau moléculaire de plaquettes de silicium. Parmi eux, l'épitaxie en phase liquide et l'épitaxie par faisceau moléculaire ne sont fondamentalement utilisées que dans les laboratoires en raison des coûts élevés. La technologie d'épitaxie du silicium la plus importante au monde est l'épitaxie en phase vapeur.

Le principe de l'épitaxie en phase vapeur consiste à utiliser certains gaz intermédiaires, tels que le tétrachlorure de silicium (SiCl4), le silicium tétrahydrogène (SiH4), le silicium trichlorosilane (SiHCL3), etc., pour générer des atomes de silicium dans les réacteurs de croissance épitaxiale de silicium et déposer le silicium. atomes sur un substrat de silicium monocristallin.

Prenons l'exemple de la réaction de réduction d'hydrogène du tétrachlorure de silicium. Le gaz tétrachlorure de silicium réagit avec l'hydrogène à une température élevée de 1200°C (l'équation chimique est : SiCl4 + 2H2 = Si + 4HCl) pour générer un atome de silicium Si solide et un sous-produit de réaction gaz HCl. Dans le même temps, des atomes de silicium se déposent sur le substrat pour former une couche épitaxiale.

3. Meilleures performances de la production de plaquettes de silicium épitaxiales

La technologie épitaxiale a d'abord été inventée pour résoudre la contradiction entre les dispositifs haute fréquence et haute puissance non seulement en réduisant la résistance, mais en exigeant également des matériaux pour résister à des tensions élevées et des courants élevés (haute résistance). Par épitaxie, une haute résistancecouche épitaxiale de plaquette de siliciumpeuvent être développés sur un substrat à faible résistance, de sorte que les dispositifs fabriqués sur les structures épitaxiales de silicium peuvent simultanément obtenir une tension de collecteur élevée et une faible résistance de collecteur.

4. Avantages de l'épitaxie du silicium

En plus de l'objectif de conception d'origine, la technologie épitaxiale présente également les avantages significatifs suivantsavantages:

4.1 Surface parfaite de silicium d'épitaxie

La couche épitaxiale peut améliorer la pureté et l'uniformité du matériau sur l'épitaxie de siliciumsurface. Par rapport aux plaquettes polies mécaniquement, les plaquettes de silicium traitées par épitaxieont une planéité de surface plus élevée, une propreté plus élevée, moins de micro-défauts et moins d'impuretés de surface, de sorte que la résistivité est plus uniforme. Il est plus facile de contrôler les particules de surface, les défauts d'empilement, les dislocations, les défauts des couches épitaxiales de silicium, etc. L'épitaxie de silicium améliore non seulement les performances du détecteur de silicium épitaxial, mais assure également la stabilité et la fiabilité du produit.

4.2 Superposition des structures

L'épitaxie peut superposer une couche épitaxiale avec différentes résistivités, éléments de dopage et concentration de dopage d'épitaxie de silicium sur le substrat d'origine, ce qui est le processus nécessaire à la fabrication de transistors à semi-conducteurs HBT (transistor bipolaire à hétérojonction), MOSFET (Metal-Oxide Semiconductor Field Effect Transistor). Dans le même temps, étant donné que l'épitaxie fournit différentes couches structurelles (résistance différente sur différentes couches), l'épitaxie est également l'une des méthodes les plus courantes pour résoudre l'effet de verrouillage et l'effet de canal court les plus courants de la technologie CMOS.

4.3 Rétro-dopage

Le dopage fait référence au processus d'introduction délibérée d'impuretés dans des matériaux purs et sans impuretés (semi-conducteurs intrinsèques) dans le processus de fabrication des semi-conducteurs pour modifier les propriétés électriques des matériaux. Le dopage peut être divisé en dopage fort, dopage léger et dopage moyen selon la quantité d'éléments dopés. Dans des circonstances normales, le dopage fort doit être supérieur au dopage léger. Grâce au processus d'épitaxie du silicium, l'échange de couches structurelles dopées ou la combinaison de plusieurs dopages peuvent être réalisés, ce qui améliore la flexibilité et les performances de la conception du dispositif sur l'épitaxie du silicium.

Pour plus d'informations, veuillez nous contacter par e-mail à victorchan@powerwaywafer.com et powerwaymaterial@gmail.com.