PAM-XIAMEN boleh membekalkan wafer epitaxial SiC, lebih banyak spesifikasi wafer sila baca:https://www.powerwaywafer.com/sic-wafer/sic-epitaxy.html.

Walaupun wafer epitaxial SiC mempamerkan ciri-ciri cemerlang dalam peranti voltan tinggi dan arus tinggi, masih terdapat beberapa jenis kecacatan yang memberi kesan negatif terhadap prestasi elektrik peranti SiC. Antaranya, lubang permukaan memberi kesan kepada pelbagai jenis peranti SiC seperti SBD dan MOS. Lubang permukaan pada wafer SiC akan menjadikan ciri peranti merosot akibat kesesakan medan elektrik. Para sarjana telah menunjukkan bahawa lubang permukaan menghasilkan arus bocor dalam SBD, tetapi punca dan mekanisme pembentukan lubang permukaan masih tidak jelas. Oleh itu, adalah penting untuk mengkaji kesan parameter pertumbuhan primitif dan epitaxial pada lubang permukaan.

1. Ekesan daripadaGbarisanTemperature padaPermukaan Pitudaripada 4H-SiC Epitaxy

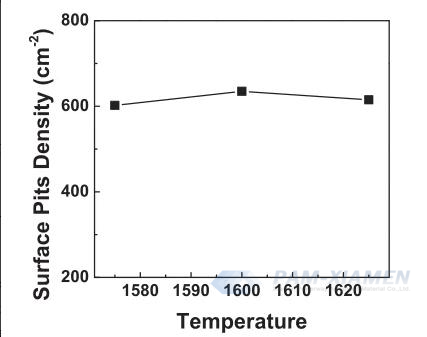

Pertama, pengaruh suhu pertumbuhan pada ketumpatan lubang permukaan telah dikaji. Di bawah keadaan nisbah C/Si 1.05, suhu pertumbuhan epitaxial 4H-SiC ialah 1575, 1600, dan 1625 ℃, masing-masing. Seperti yang ditunjukkan dalam Rajah 1, suhu epitaxial tidak mempunyai kesan ketara ke atas ketumpatan lubang. Ketumpatan kecacatan cair tidak menunjukkan arah aliran menurun yang ketara dengan perubahan suhu. Jika suhu terus meningkat atau turun, ia akan menyebabkan masalah lain seperti kecacatan segi tiga dan tandan langkah.

Rajah.1 Kesan suhu pertumbuhan pada lubang permukaan epitaksi SiC

2. Pengaruh daripadaC/SiRatio padaSiC Epitaxial SurfacePitu

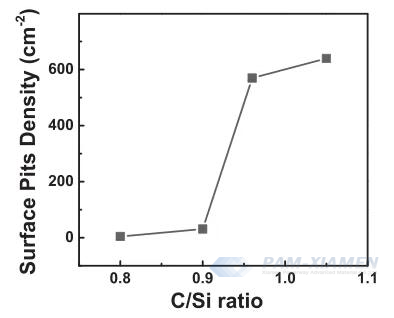

Kemudian, kesan nisbah C/Si terhadap ketumpatan lubang permukaan telah dikaji. Seperti yang ditunjukkan dalam Rajah 2, ketumpatan lubang permukaan berkurangan dengan penurunan nisbah C/Si. Apabila nisbah C/Si meningkat kepada 1.05, ketumpatan pit terus meningkat, manakala apabila nisbah C/Si menurun kepada 0.9, ketumpatan pit dengan cepat berkurangan kepada sekitar 30/cm2. Hasilnya adalah serupa dengan kajian terdahulu. Apabila nisbah C/Si tinggi, suasana C yang kaya adalah kondusif untuk pembentukan lubang permukaan, dan bentuk lubang permukaan secara beransur-ansur membentuk lubang dalam. Walau bagaimanapun, apabila nisbah C/Si terlalu rendah, ia boleh menyebabkan peningkatan kepekatan latar belakang dan penurunan dalam Si. Oleh itu, adalah perlu untuk mencari parameter lain untuk menekan ketumpatan lubang permukaan SiC. Berdasarkan nisbah C/Si 0.9, teruskan mengoptimumkan ketumpatan lubang wafer 4H-SiC Epi.

Rajah 2 Pengaruh nisbah C/Si pada lubang permukaan epitaxial 4H-SiC

3. Cl/SiRatioKesanpadaSurfacePdaripadaEpilayer 4H-SiC

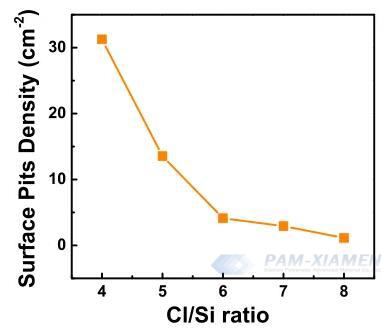

Penyiasatan lanjut telah dijalankan ke atas kesan nisbah Cl/Si pada lubang permukaan, dengan nisbah C/Si 0.9, seperti yang ditunjukkan dalam Rajah 3. Apabila nisbah Cl/Si meningkat, ketumpatan lubang permukaan berkurangan. Apabila nisbah Cl/Si ialah 8, ketumpatan lubang permukaan berkurangan kepada 1 cm-2. Apabila nisbah Cl/Si meningkat, atom Cl boleh mengurangkan nukleasi seragam atom Si dengan berkesan, membentuk persekitaran yang kaya dengan Si pada permukaan cip. Oleh itu, nisbah C/Si berkesan pada permukaan substrat telah dikurangkan, pertumbuhan aliran langkah dipertingkatkan, dan pembentukan kecacatan seperti lubang telah ditindas.

Rajah 3 Kesan nisbah Cl/Si pada lubang permukaan epitaxial 4H-SiC

Semasa proses pertumbuhan epitaxial 4H-SiC, nisbah C/Si dan nisbah Cl/Si mempunyai kesan yang ketara ke atas lubang permukaan. Nisbah C/Si yang lebih rendah dan nisbah Cl/Si yang lebih tinggi akan membentuk persekitaran yang kaya dengan silikon pada permukaan wafer semasa proses pertumbuhan, yang penting untuk mengurangkan lubang permukaan pada wafer epitaxial 4H-SiC. Dengan mengoptimumkan proses, ketumpatan lubang dikurangkan kepada di bawah 1/cm2, dan ketumpatan kecacatan maut permukaan (termasuk kecacatan segi tiga, kecacatan lobak merah, jatuh, dll.) dipastikan berada dalam julat tertentu, mendapatkan wafer epitaxial SiC berkualiti tinggi, memenuhi keperluan peranti kuasa SiC.

Untuk maklumat lanjut, sila hubungi kami e-mel divictorchan@powerwaywafer.com dan powerwaymaterial@gmail.com.