PAM-XIAMEN có thể cung cấp tấm wafer SiC, vui lòng đọc thêm thông số kỹ thuật của tấm wafer:https://www.powerwaywafer.com/sic-wafer/sic-epitaxy.html.

Mặc dù các tấm wafer epiticular SiC thể hiện các đặc tính tuyệt vời trong các thiết bị điện áp cao và dòng điện cao, nhưng vẫn có một số loại khuyết tật có tác động tiêu cực đến hiệu suất điện của thiết bị SiC. Trong số đó, các hố bề mặt có tác động lên các loại thiết bị SiC khác nhau như SBD và MOS. Các vết rỗ bề mặt trên wafer SiC sẽ làm cho các đặc tính của thiết bị xấu đi do điện trường đông đúc. Các học giả đã chỉ ra rằng các hố bề mặt tạo ra dòng rò trong SBD, nhưng nguyên nhân và cơ chế hình thành các hố bề mặt vẫn chưa rõ ràng. Vì vậy, việc nghiên cứu ảnh hưởng của các thông số tăng trưởng nguyên thủy và epiticular lên các hố bề mặt là rất quan trọng.

1. Eảnh hưởng củaGchèo kéoTnhiệt độ trênBề mặt Pcủa nócủa Epitaxy 4H-SiC

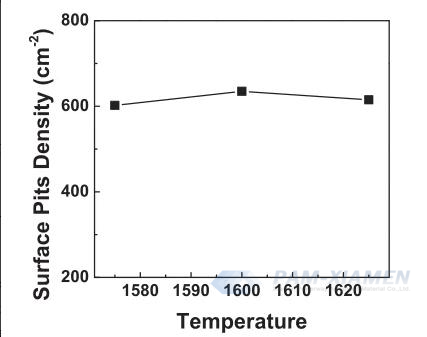

Đầu tiên, ảnh hưởng của nhiệt độ tăng trưởng đến mật độ hố bề mặt đã được nghiên cứu. Trong điều kiện tỷ lệ C/Si là 1,05, nhiệt độ tăng trưởng epiticular của 4H-SiC lần lượt là 1575, 1600 và 1625oC. Như được hiển thị trong Hình 1, nhiệt độ epiticular không ảnh hưởng đáng kể đến mật độ hố. Mật độ khuyết tật nóng chảy không cho thấy xu hướng giảm đáng kể khi thay đổi nhiệt độ. Nếu nhiệt độ tiếp tục tăng hoặc giảm sẽ gây ra các vấn đề khác như khuyết tật hình tam giác và hiện tượng bó bước.

Hình 1 Ảnh hưởng của nhiệt độ tăng trưởng đến các hố bề mặt của epit Wax SiC

2. Ảnh hưởng củaC/SiRbật lênSiC Epiticular Sbề mặtPcủa nó

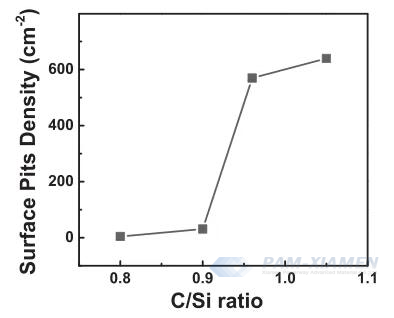

Sau đó, ảnh hưởng của tỷ lệ C/Si đến mật độ hố bề mặt được nghiên cứu. Như được hiển thị trong Hình 2, mật độ của các hố bề mặt giảm khi tỷ lệ C/Si giảm. Khi tỷ lệ C/Si tăng lên 1,05, mật độ hố càng tăng, trong khi khi tỷ lệ C/Si giảm xuống 0,9, mật độ hố giảm nhanh xuống khoảng 30/cm2. Kết quả tương tự như nghiên cứu trước đây. Khi tỷ lệ C/Si cao, bầu không khí giàu C có lợi cho việc hình thành các hố bề mặt và hình dạng của các hố bề mặt dần dần hình thành các hố sâu. Tuy nhiên, khi tỷ lệ C/Si quá thấp có thể làm tăng nồng độ nền và giảm Si. Vì vậy, cần phải tìm kiếm các thông số khác để hạn chế hơn nữa mật độ hố bề mặt SiC. Trên cơ sở tỷ lệ C/Si là 0,9, tiếp tục tối ưu hóa mật độ hố của tấm wafer 4H-SiC Epi.

Hình 2 Ảnh hưởng của tỷ lệ C/Si đến các hố bề mặt epiticular 4H-SiC

3. Cl/SiRatioVa chạmTRÊNSbề mặtPcủa nóLớp biểu bì 4H-SiC

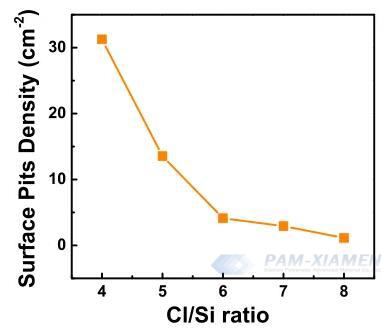

Nghiên cứu sâu hơn đã được tiến hành về ảnh hưởng của tỷ lệ Cl/Si trên các hố bề mặt, với tỷ lệ C/Si là 0,9, như trong Hình 3. Khi tỷ lệ Cl/Si tăng, mật độ của các hố bề mặt giảm. Khi tỷ lệ Cl/Si là 8 thì mật độ các vết rỗ trên bề mặt giảm xuống còn 1 cm-2. Khi tỷ lệ Cl/Si tăng lên, các nguyên tử Cl có thể làm giảm hiệu quả quá trình tạo mầm đồng nhất của các nguyên tử Si, tạo thành môi trường giàu Si trên bề mặt chip. Do đó, tỷ lệ C/Si hiệu quả trên bề mặt chất nền bị giảm, sự tăng trưởng của dòng chảy theo bậc được tăng cường và sự hình thành các khuyết tật dạng hố bị ngăn chặn.

Hình 3. Ảnh hưởng của tỷ lệ Cl/Si đến bề mặt epiticular 4H-SiC

Trong quá trình tăng trưởng epiticular 4H-SiC, tỷ lệ C/Si và tỷ lệ Cl/Si có tác động đáng kể đến các hố bề mặt. Tỷ lệ C/Si thấp hơn và tỷ lệ Cl/Si cao hơn sẽ tạo thành môi trường giàu silicon trên bề mặt tấm bán dẫn trong quá trình tăng trưởng, điều này rất quan trọng để giảm vết rỗ trên bề mặt trên tấm bán dẫn epiticular 4H-SiC. Bằng cách tối ưu hóa quy trình, mật độ hố đã giảm xuống dưới 1/cm2và mật độ khuyết tật nghiêm trọng trên bề mặt (bao gồm khuyết tật hình tam giác, khuyết tật cà rốt, té ngã, v.v.) được đảm bảo nằm trong phạm vi nhất định, thu được tấm wafer SiC chất lượng cao, đáp ứng yêu cầu của thiết bị điện SiC.

Để biết thêm thông tin, xin vui lòng liên hệ với chúng tôi email tạivictorchan@powerwaywafer.com và powerwaymaterial@gmail.com.