Vật liệu wafer SiC có dải rộng, độ linh động bão hòa electron cao và tính chất nhiệt tuyệt vời, có triển vọng ứng dụng lớn trong các thiết bị nhiệt độ cao, tần số cao và công suất cao. Chất lượng bề mặt của bề mặt Si ảnh hưởng trực tiếp đến chất lượng của màng mỏng epiticular SiC và hiệu suất của các thiết bị của nó. Tuy nhiên, các khuyết tật trên bề mặt C có thể làm tăng mật độ sai lệch tinh thể, điều này cũng có thể dẫn đến sự hình thành các khuyết tật trong lớp tăng trưởng của màng mỏng epiticular và ảnh hưởng đến hiệu suất của thiết bị. Do đó, cả bề mặt Si và C của tấm wafer SiC đều yêu cầu bề mặt của chúng phải cực kỳ mịn, không có khuyết tật và không bị hư hại.

PAM-Hạ Môncó thể cung cấp các tấm SiC mặt phẳng Carbon (C) được xử lý CMP cho các nghiên cứu chuẩn bị thiết bị, như tụ điện MOS, các thông số cụ thể vui lòng liên hệ với nhóm bán hàng của chúng tôi:victorchan@powerwaywafer.com

1.Snghiên cứu về CMPTsự tái chiếmbề mặt Sivà CSbề mặttrên chất nền SiC

K2S2O được sử dụng làm chất oxy hóa và hạt nano Al2O3 làm chất mài mòn để so sánh hiệu quả đánh bóng CMP trên bề mặt Si và C của chất nền 6H-SiC. XPS được sử dụng để phân tích cơ chế ảnh hưởng của các mặt tinh thể khác nhau đến hiệu ứng đánh bóng CMP của chúng. Có sự khác biệt đáng kể về hiệu quả đánh bóng CMP giữa bề mặt Si và C của tấm wafer 6H-SiC.

Tốc độ loại bỏ vật liệu trên bề mặt Si đạt giá trị tối đa 349nm/h ở pH=6, trong khi tốc độ loại bỏ vật liệu trên bề mặt C đạt giá trị tối đa 1184 nm/h ở pH=2. Tuy nhiên, mặt Si và C được đánh bóng tương đối mịn, với giá trị độ nhám Ra lần lượt là 0,58nm và 0,55nm.

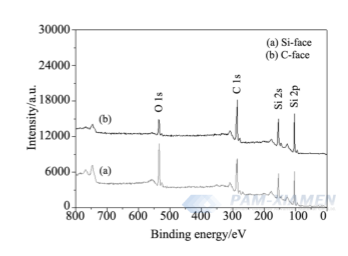

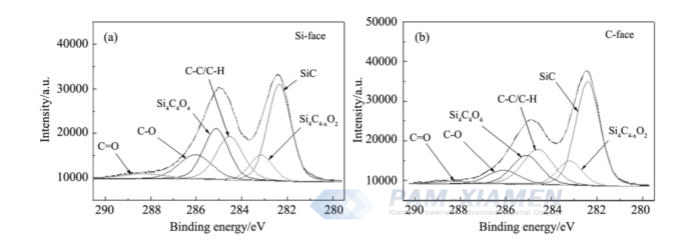

Sau khi đánh bóng, phổ XPS của bề mặt Si và C nhìn chung tương tự nhau, nhưng có sự khác biệt đáng kể về thành phần nguyên tử giữa bề mặt Si và C. Hình 1 cho thấy nồng độ nguyên tử O1 và tỷ lệ C/Si và O/Si trên bề mặt Si cao hơn trên bề mặt C, nhưng nồng độ nguyên tử C1 và Si2p trên bề mặt C cao hơn thế. trên bề mặt Si. Hơn nữa, tỷ lệ C/Si trên cả hai bề mặt cao hơn tỷ lệ cân bằng hóa học thông thường của chúng là 1. Cường độ cực đại của năng lượng liên kết Si-C trên mặt phẳng C cao hơn trên mặt phẳng Si, nhưng hàm lượng các sản phẩm oxy hóa ( chẳng hạn như Si4-C4-x-O2, Si4-C4-O4, CO và C=O) trên mặt phẳng Si cao hơn trên mặt phẳng C, như trong Hình 2. Điều này chỉ ra rằng các oxit trên mặt phẳng C dễ loại bỏ hơn trên mặt phẳng Si, do đó mặt phẳng C dễ dàng đạt được tốc độ loại bỏ vật liệu cao hơn trên mặt phẳng Si.

Hình 1 Phổ XPS của bề mặt được đánh bóng của wafer 6H-SiC

Hình 2 Phổ C1 của các bề mặt được đánh bóng của bề mặt 6H-SiC (a) Si; (b) Mặt chữ C

2. Nghiên cứu tụ điện MOS trên wafer SiC mặt Si và mặt C

Các học giả đã nghiên cứu mối tương quan giữa cấu trúc nguyên tử và hiệu suất điện của tụ điện SiC MOS tương ứng, đồng thời thảo luận về các tác động bên trong và bên ngoài của cấu trúc giao diện và các khiếm khuyết về điện đối với điều chế bù băng tần.

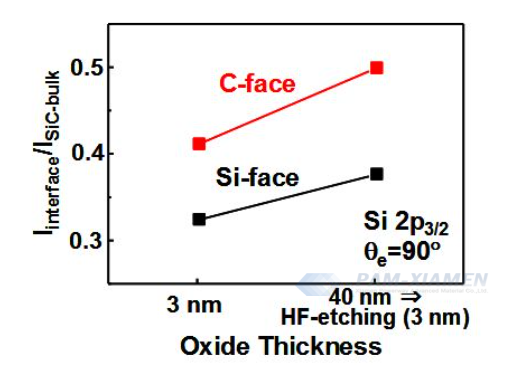

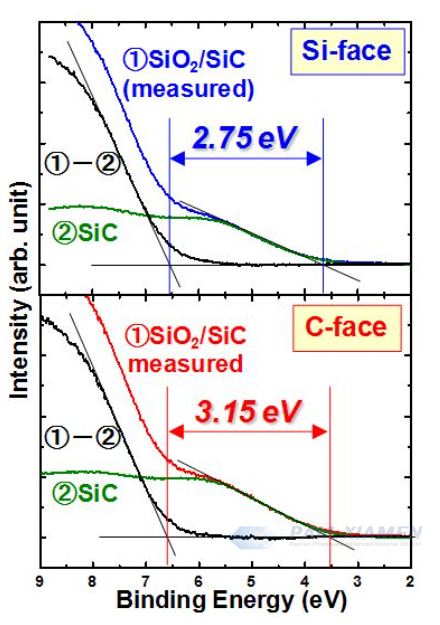

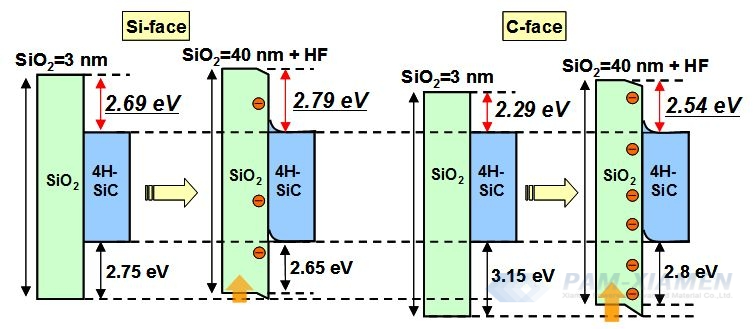

Thu được cấu trúc dải của cấu trúc SiO2/SiC được chế tạo ở các điều kiện khác nhau. Kết quả chỉ ra rằng độ lệch dải dẫn xác định dòng rò cổng của thiết bị SiC MOS và độ tin cậy của oxit cổng thu được chủ yếu phụ thuộc vào hướng của chất nền và độ dày oxit. Do sự dịch chuyển dải dẫn nhỏ hơn được thể hiện bởi oxit mỏng trên chất nền bề mặt C so với chất nền bề mặt Si, nên kết luận rằng độ tin cậy giảm của các thiết bị SiC MOS được sản xuất trên mặt C là một vấn đề cố hữu, có thể là do đến sự khác biệt về độ âm điện giữa nguyên tử Si và nguyên tử C liên kết với nguyên tử O tại bề mặt phân cách.

Ngoài ra, khi xem xét sự tích tụ của các điện tích âm cố định tại bề mặt phân cách SiO2/SiC, sự gia tăng dịch chuyển dải dẫn của các oxit dày trên nền Si và C có thể được giải thích bằng sự điều chế dải không nội tại gây ra bởi các khiếm khuyết ở bề mặt.

Từ góc độ giảm rò rỉ cổng, độ lệch băng tần mở rộng này của các thiết bị MOS dày được ưu tiên hơn, nhưng các khiếm khuyết về điện sẽ có tác động tiêu cực đến hiệu suất và độ tin cậy của thiết bị. Do đó, các chiến lược cơ bản như áp dụng các oxit cổng lắng đọng và sử dụng các cấu trúc xếp chồng lên nhau trong kỹ thuật băng tần là rất cần thiết để sử dụng các thiết bị MOS trên SiC mặt C.

Hình 3 Phổ biến đổi Si 2p3/2 trong tổng lượng trạng thái oxit trung gian từ bề mặt phân cách oxit phát triển trên các mặt SiC (0001) Si và C

Hình 4. Phổ dải hóa trị đo và giải mã của các cấu trúc SiO2/SiC hình thành trên nền Si và C đối mặt với 4H-SiC, cho thấy độ dịch chuyển dải hóa trị của SiO2/SiC trên nền bề mặt C cao hơn khoảng 0,4 eV so với trên bề mặt Si .

Hình 5 Sơ đồ dải năng lượng của cấu trúc 4H-SiC mặt phẳng SiO2/Si hoặc C bằng phân tích synchrotron XPS. Đo độ dịch chuyển dải hóa trị tại giao diện SiO2/SiC được hình thành trong các điều kiện khác nhau.

Người giới thiệu:

1. CHEN Guo-mei, NI Zi-feng,QIAN Shan-hua , LIU Yuan-xiang,DU Chun-kuan, ZHOU Ling, XU Yi-e

vi, ZHAO Yong-wu. Ảnh hưởng của các mặt phẳng tinh thể khác nhau đến hiệu suất CMP của wafer SiC

2. Heiji Watanabe, Takuji Hosoi. Các khía cạnh cơ bản của quá trình oxy hóa cacbua silic

Để biết thêm thông tin, xin vui lòng liên hệ với chúng tôi email tạivictorchan@powerwaywafer.com và powerwaymaterial@gmail.com.