PAM-XIAMEN은 SiC 웨이퍼를 제공할 수 있으며, 구체적인 사양과 매개변수는 다음에서 확인할 수 있습니다.https://www.powerwaywafer.com/sic-wafer

4H-SiC 단결정은 넓은 밴드갭, 높은 캐리어 이동도, 높은 열 전도성 및 우수한 안정성과 같은 우수한 특성을 가지고 있습니다. 이는 고전력 전자공학, 무선 주파수/마이크로파 전자공학, 양자 정보 분야에서 폭넓은 응용 가능성을 갖고 있습니다. 수년간의 개발 끝에 6인치 4H SiC 단결정 기판과 균일한 에피택셜 박막이 산업적으로 적용되었습니다. 그러나 4H SiC 웨이퍼의 총 전위 밀도는 여전히 10만큼 높습니다.3~104센티미터-2이는 4H-SiC 웨이퍼의 잠재력을 최대한 발휘하는 데 방해가 됩니다. 전위는 4H-SiC 웨이퍼 및 장치의 특성에 어떤 영향을 줍니까? 구체적인 분석은 다음과 같습니다.

1. 4H-SiC 웨이퍼 및 소자의 전기적 특성에 대한 전위의 영향

연구에서는 4H-SiC 웨이퍼 및 장치의 성능과 기능 영역 내 전위 분포 사이의 관계를 분석하여 전위의 존재가 장치 성능에 부정적인 영향을 미칠 수 있음을 시사했습니다. 따라서 전위 자체의 전기적 특성을 연구하는 것은 장치에서 전위의 거동을 이해하는 데 큰 의미가 있습니다.

1.1 4H-SiC 기판의 전기적 특성에 대한 전위의 영향

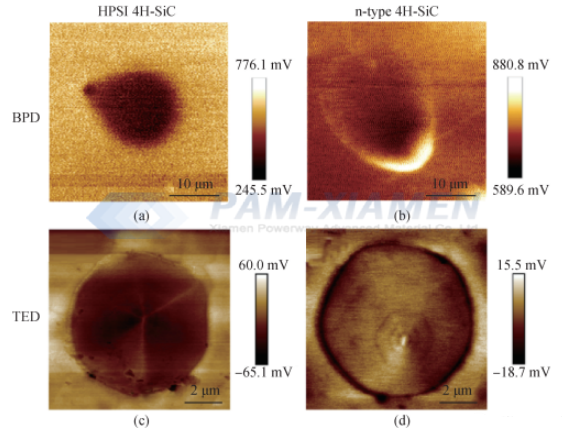

용융 알칼리 부식과 KPFM(켈빈 탐침 힘 현미경)을 결합하면 TED(스레딩 가장자리 전위) 및 BPD(기저 평면 전위)가 HPSI(고순도 반절연) 4H SiC 기판 및 도너 상태에서 수용체 상태를 나타내는 것을 관찰할 수 있습니다. n형 4H SiC 기판(그림 1 참조) 도핑 농도가 낮은 4H SiC 에피택시층에서는 관통 전위가 억셉터 특성을 나타내는 것으로도 밝혀졌다. 첫 번째 원리 계산에 따르면 TED와 BPD는 결함 에너지 준위를 도입하며 가전자대 하단 근처의 에너지 준위는 빈 대역이라는 사실이 밝혀졌습니다. 불순물 원자와 같은 깊은 수준의 결함이 우세하기 때문에 탄소 결손(VC) 또는 공석 쌍(VC-V시) HPSI 4H SiC에서는 전위에 의해 도입된 공극 밴드가 깊은 수준의 전자를 수용할 수 있으며 전위는 억셉터 특성을 나타냅니다. n형 기판에서 계산에 따르면 N 원자는 TED 및 BPD 전위에 결합하는 데 더 안정적이므로 N 원자는 전위 근처에서 응집되는 경향이 있습니다. 전도성 기판에서 도핑된 원자가 우세하기 때문에 N 원자의 집합은 전위의 도너 특성을 유발할 수 있습니다.

그림 1 HPSI 및 n형 4H-SiC에서 BPD 및 TED의 표면 전위 분포

1.2 4H-SiC 소자의 전기적 특성에 대한 전위의 영향

TSD(Threading Screw Dislocation)로 인한 마이크로 피트를 스캔한 결과 C-AFM 테스트 결과 마이크로 피트 바닥의 전류가 크게 증가한 반면, 마이크로 피트 내부 다른 영역의 표면 전류는 크게 다르지 않은 것으로 나타났습니다. 마이크로 구덩이 외부에서. 이는 4H SiC에서 TSD의 전위선이 누출 효과를 향상시킨다는 것을 나타냅니다. 또한, 재결합 중심으로서의 전위는 4H-SiC 전력 소자에서 전자 정공 재결합을 유발할 수 있으며 소자 신뢰성 저하로 이어질 수도 있습니다.

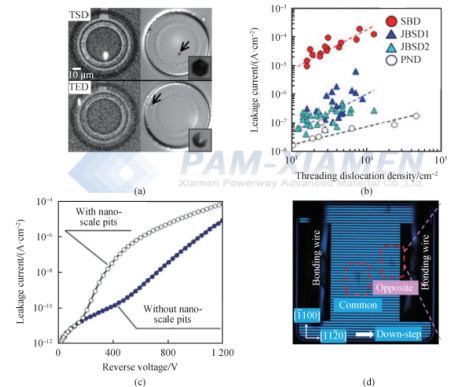

전위선은 소자 성능에 영향을 미칠 뿐만 아니라, 전위선으로 인한 외부 계단 흐름의 교란으로 인해 에피택시층 표면에 나노 수준 깊이의 표면 미세 피트를 유발합니다. 마이크로 피트의 존재도 장치 성능에 영향을 미칠 수 있습니다. 예를 들어, 고압에서는 TD(threading dislocation)로 인해 마이크로 크레이터 위치에 마이크로 플라즈마가 나타나며, 이는 마이크로 크레이터 위치의 게이트 산소가 먼저 분해됨을 나타냅니다. 마이크로 피트의 존재는 소수 캐리어의 수명 감소, 역방향 누설 전류 증가, 순방향 전압 감소로 이어질 수 있으며, 이는 4H SiC 기반 쇼트키 배리어 다이오드(SBD), pn 접합 다이오드에 악영향을 미칩니다. (PND) 및 애벌런치 포토다이오드(그림 2(a) 및 (b) 참조).

따라서 일부 연구자들은 현재 전위가 소자 성능에 미치는 영향은 주로 마이크로 피트에 의해 발생하고 전위 라인 자체의 영향은 부차적이라고 생각합니다. 시뮬레이션과 실험을 통해 마이크로 피트의 존재를 배제하면 4H-SiC 기반 디바이스에 대한 TSD의 영향을 줄일 수 있다는 것이 밝혀졌습니다(그림 2(c) 참조). BPD는 4H-SiC의 복합 센터 역할도 할 수 있습니다. 4H-SiC 양극 장치에서 작동할 때 전기 주입으로 인해 실리콘 코어의 불완전 전위가 미끄러져 적층 결함 확장이 발생하고 장치의 순방향 및 역방향 성능에 심각한 영향을 미칠 수 있습니다. 일반적으로 BPD에서 실리콘 코어의 불완전 전위로 인한 적층 결함은 기판과 에피택셜 층 사이의 경계면에서 발생하고 에피택셜 층의 표면에서 바깥쪽으로 확장되는 것으로 믿어집니다. BPD에서 두 개의 불완전 전위의 방향성 움직임을 고려하면 BPD로 인한 적층 결함의 확장은 복잡합니다. 연구에 따르면 BPD로 인한 적층 결함은 기판과 에피택셜 층 사이의 경계면 쪽으로 이동할 수도 있습니다(그림 2(d) 참조).

그림 2 4H-SiC 전력 장치의 누설 전류 및 4H-SiC의 적층 결함 확장에 대한 전위의 영향: (a) 애벌런치 다이오드의 EL 이미지(왼쪽) 및 KOH 부식 용융 후 DIC 이미지(오른쪽); (b) 서로 다른 장치의 누설 전류와 TD 밀도 간의 관계; (c) 4H-SiC 다이오드의 역방향 누설 거동과 나노 피트에 대한 의존성; (d) 420nm 필터로 관찰한 4H SiC PIN 장치의 EL 이미지

2. 4H-SiC의 광학 특성에 대한 전위의 영향

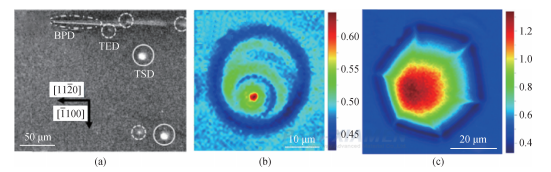

방사성 재결합 센터로서 4H-SiC의 전위는 광발광을 나타내며 전위 광발광(PL)의 대비는 소수 캐리어의 수명에 따라 달라집니다. 결정 내 깊은 준위 결함의 농도가 낮으면 소수 캐리어의 수명이 길어지고 충분한 소수 캐리어가 전위 영역으로 이동하여 재결합하여 빛을 방출하게 됩니다. 이때 전위영역의 발광세기는 다른 영역에 비해 높아 밝은 점으로 나타난다. 결정 내 깊은 준위 결함의 농도가 높으면 소수 캐리어의 수명이 낮아지고, 가까운 깊은 준위 결함과 결합하여 발광하게 됩니다. 전위에서의 재결합이 억제되고 전위 영역의 발광 강도가 다른 영역에 비해 약해 어두운 점을 나타냅니다. 실험에 따르면 PL 테스트에서 소수 캐리어의 수명이 0.5μs 미만인 4H-SiC의 경우 대부분의 소수 캐리어가 전위로 이동할 수 없으며 소수의 소수 캐리어가 고유 결함에 의해 포착되는 것으로 나타났습니다. 전위는 PL 표면 스캔 이미지에서 큰 대비를 나타내지 않습니다. 소수 캐리어의 수명이 0.5μs보다 크면 전위에서 전자 정공 재결합이 전위의 대비를 다른 영역과 크게 구별할 수 있습니다.

TSD와 TED는 4H-SiC의 PL 표면 스캔 이미지에서 서로 다른 크기의 어두운 점과 밝은 점을 나타냅니다. TED와 TSD의 고유 PL 방출 피크는 각각 600nm와 800-850nm에 위치합니다. BPD는 4H-SiC의 PL 표면 스캔 이미지에서 어둡거나 밝은 선으로 나타납니다(그림 3(a) 참조). BPD의 PL 방출 피크는 BPD를 구성하는 불완전 전위 및 적층 결함의 PL 방출 피크에서 발생합니다. 실리콘 코어 불완전 전위, 탄소 코어 불완전 전위, 적층 결함의 방출 피크는 각각 670~700nm, 720~850nm, 420nm에 위치합니다. 방출된 빛의 파장을 조정하면 단일 불완전 전위와 적층 결함을 별도로 표시할 수 있습니다.

최근 연구자들은 각각 TED 및 TSD 부식 피트의 발광 강도를 나타내는 그림 3(b) 및 (c)에 표시된 것처럼 TD가 4H-SiC의 D1 발광을 향상시킬 수 있음을 발견했습니다. 이는 D1 발광의 강도가 4H-SiC 기판과 에피택셜 층의 전위 밀도와 분포도 반영할 수 있음을 의미합니다.

그림 3 4H-SiC에서 전위의 발광 특성: (a) 900nm 대역통과 필터를 사용하여 얻은 4H SiC 에피택시 박막의 마이크로 영역 PL 표면 스캔 이미지; (b) TED 미세영역 PL 표면 스캔 이미지 및 (c) 450nm~750nm의 방출에서 얻은 N형 4H-SiC 기판의 TSD 미세영역 PL 표면 스캔 이미지.

재료 크기를 늘리고 전위 밀도를 줄이는 것이 4H-SiC 기판 및 에피택셜 박막 개발의 전반적인 방향입니다. 전위 밀도를 줄이려면 열장 및 유동장 설계를 최적화하고, 종자 결정 또는 기판 처리 기술을 설계하고, 단결정 또는 에피택셜 공정 기술을 최적화하여 전위 밀도를 낮추는 것이 필요합니다. 한편, 점점 성숙해지는 공정 기술을 기반으로 낮은 전위 밀도를 줄이기 위해 다양한 유형의 전위 간의 변형 또는 반응을 촉진하는 방법에 대한 심층적인 연구가 필요합니다. 전위의 성능을 조절하는 측면에서, 전위와 함께 불순물과 점결함 사이의 반응을 촉진하여 결함 에너지 수준 위치와 전위의 동적 거동을 조정하는 방법에 대한 추가 연구가 필요합니다.

참조:

Jiajun Li, Guang Yang, Xiaoshuang Liu, Hao Luo, Lingbo Xu, Yiqiang Zhang, Can Cui, Xiaodong Pi, Deren Yang 및 Rong Wang

4H 실리콘 카바이드의 전위

자세한 내용은 이메일로 문의해 주세요.victorchan@powerwaywafer.com 과 powerwaymaterial@gmail.com.