SiC를 에피 택시

- 기술

제품 설명

SiC를 에피 택시

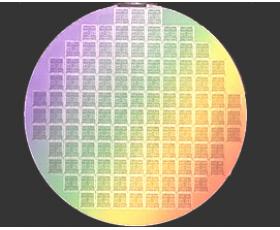

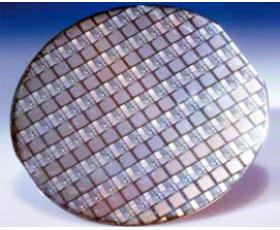

PAM-XIAMEN은 탄화규소 장치 개발을 위해 6H 또는 4H 기판에 맞춤형 박막(탄화규소) SiC 에피택시를 제공합니다. SiC 에피 웨이퍼는 주로 SBD, JBS, PIN, MOSFET, JFET, BJT, GTO, IGBT 등 600V~3300V 전력소자 제조에 사용된다. 탄화규소 웨이퍼를 기판으로 하여 화학기상증착(CVD) ) 방법은 일반적으로 웨이퍼에 단결정 층을 증착하여 에피택셜 웨이퍼를 형성하는 데 사용됩니다. 그 중 SiC 에피택시는 전도성 탄화규소 기판 위에 탄화규소 에피택시 층을 성장시켜 제조되며, 이는 추가로 전력 소자로 제작할 수 있습니다.

1. SiC 에피 택시 사양 :

| 항목 | 명세서 | 일반적인 값 |

| 폴리 형 | 4H | — |

| 대한 오프 오리엔테이션 | 4 ℃에서 오프 | — |

| <11 2_ 0> | ||

| 전도도 | n 형 | — |

| 도펀트 | 질소 | — |

| 캐리어 농도 | 5E15-2E18 cm-3 | — |

| 허용 오차 | ± 25 % | ± 15 % |

| 일률 | 2 '(이 50.8mm) <10 % | 7 % |

| 3 "(76.2mm) <20 % | 10 % | |

| 4 "(100mm) <20 % | 15 % | |

| 두께 범위 | 5 ~ 15 μm의 | — |

| 허용 오차 | ± 10 % | ± 5 % |

| 일률 | 2 "<5 % | 2 % |

| 3 '<7 % | 3 % | |

| 4 "<10 % | 5 % | |

| 대형 포인트 결함 | 2 "<30 | 2 "<15 |

| 3 "<60 | 3 "<30 | |

| 4 "<90 | 4 "<45 | |

| 에피 결함 | ≤20 cm-2 | ≤10 cm-2 |

| 단계 뭉침 | ≤2.0nm (Rq가) | ≤1.0nm (Rq가) |

| (거) |

50.8 및 76.2mm의 경우 2mm 가장자리 제외, 100.0mm의 경우 3mm 가장자리 제외

• 두께 및 캐리어 농도에 대한 모든 측정 지점의 평균 (5 페이지 참조)

• N 형 에피 층 <20 미크론 앞에 n 형, 1E18, 0.5 미크론 버퍼층이 있습니다.

• 모든 두께에서 모든 도핑 밀도를 사용할 수있는 것은 아닙니다

• 균일 성 : 표준 편차 (σ) / 평균

• epi-parameter에 대한 특별한 요구 사항은 요청시

2. SiC 에피택시 도입

실리콘 카바이드 에피 택셜 웨이퍼가 필요한 이유는 무엇입니까? 기존의 실리콘 전력 장치 제조 공정과 다르기 때문에 실리콘 카바이드 전력 장치는 실리콘 카바이드 단결정 재료에서 직접 제조할 수 없습니다. 고품질 에피택셜 재료는 전도성 단결정 기판에서 성장해야 하며, SiC 에피택시 웨이퍼에서 제조되는 다양한 장치가 필요합니다.

SiC 에피택시 성장을 위한 주요 에피택셜 기술은 화학 기상 증착(CVD)이며, 이는 SiC 에피택시 반응기 단계 흐름의 성장을 통해 특정 두께와 도핑된 탄화규소 에피택시 물질을 구현합니다. 실리콘 카바이드 전력 장치 제조 요구 사항 및 내전압 수준의 개선으로 SiC 에피 웨이퍼는 결함이 적고 에피택시가 두꺼운 방향으로 계속 발전하고 있습니다.

최근 몇 년 동안 얇은 탄화규소 에피택셜 재료(<20μm)의 품질이 지속적으로 향상되었습니다. 에피택셜 재료의 미세소관 결함이 제거되었습니다. 그러나 드롭, 삼각형, 당근, 나사 전위, 기저면 전위, 심층 결함 등과 같은 SiC 에피택시 결함은 장치 성능에 영향을 미치는 주요 요인이 됩니다. SiC 에피택시 공정의 발전으로 에피택시층의 두께는 과거 수 μm, 수십 μm에서 현재 수십 μm, 수백 μm로 발전했다. Si에 비해 SiC의 장점 덕분에 SiC 에피택시 시장은 빠르게 성장하고 있습니다.

탄화규소 소자는 에피택셜 재료로 제작되어야 하므로 기본적으로 모든 탄화규소 단결정 재료는 에피택셜 재료를 성장시키기 위한 SiC 에피택셜 필름으로 사용됩니다. 탄화규소 에피택셜 재료의 기술은 국제적으로 빠르게 발전했으며, 가장 높은 에피택셜 두께는 250μm 이상에 이릅니다. 그 중 20μm 이하의 에피택시 기술은 성숙도가 높다. 표면 결함 밀도는 1/cm2 미만으로 감소되었으며 전위 밀도는 105/cm2에서 103/cm2로 감소되었습니다. 기본 평면의 전위 변환율은 100%에 가깝고, 이는 탄화규소 장치의 대규모 생산을 위한 에피택셜 재료의 요구 사항을 기본적으로 충족했습니다.

최근에는 국제 30μm~50μm 에피택시 재료 기술도 빠르게 발전하고 있지만 SiC 에피 시장 수요의 한계로 인해 산업화의 진행이 더뎠다. 현재 산업화 회사는 Cree SiC 에피택시, PAM-XIAMEN SiC 에피택시, Dow Corning SiC 에피택시 등을 포함하여 실리콘 카바이드 에피택시 재료를 배치로 제공할 수 있습니다.

3. 테스트 방법

1 위. 캐리어 농도 : 순 도핑 수은 프로브를 이용하여 CV Afer 즉 어 크로스 평균치로한다.

2 번. 두께 : 두께 FTIR을 사용하여 웨이퍼를 가로 지르는 평균 값으로 결정된다.

No.3.Large 점 결함 : 현미경 올림푸스 광학 현미경에 100X에서 수행 검사, 또는 비교.

No.4. Epi 결함 KLA-Tencor Candela CS20 광학 표면 분석기 또는 SICA에서 수행 된 검사 또는 결함 맵.

5 번. 단계 뭉침 스텝 뭉침 거칠기가 10 ㎛의 x10μm 영역을 AFM (원 자간 력 현미경)으로되어 scaned

3-1:큰 점 결함 설명

비 보조 눈에 명확한 모양을 전시하고 있습니다 결함>에서 50microns. 이러한 기능은 스파이크, 부착 입자, 칩 andcraters을 포함한다. 3mm보다 큰 점결함 떨어져 하나의 결함으로 간주.

3-2: 에피택시 결함 설명

SiC 에피택시 결함에는 3C 내포물, 혜성 꼬리, 당근, 입자, 실리콘 방울 및 몰락이 포함됩니다.

4. SiC 에피택시 웨이퍼의 적용

역률 보정 (PFC)

PV 인버터 및 UPS (무정전 전원 장치), 인버터

모터 드라이브

출력 정류

하이브리드 또는 전기 자동차

600V, 650V, 1200V, 1700V와 SiC 쇼트 키 다이오드는, 3300V 사용할 수 있습니다.

아래의 분야별 응용 프로그램을 참조하십시오 :

| 들 | 무선 주파수 (RF) | 전력 장치 | LED |

| 자료 | 실드 모스 | 시 | GaN / Al2O3 |

| 갈륨 비소 | GaN / Si | GaN / Si | |

| GaN / SiC | SiC / SiC | GaN / SiC | |

| GaN / Si | Ga203 | / | |

| 장치 | SiC 기반 GaN HEMT | SiC 기반 MOSFET SiC 기반 BJT SiC 기반 IGBT SiC 기반 SBD |

/ |

| 신청 | 레이더, 5G | 전기차 | 무 접점 조명 |

5. Epi 레이어가 있는 기계식 웨이퍼: 낮은 휨과 뒤틀림이 있는 웨이퍼가 필요한 공정 모니터링과 같이 사용할 수 있습니다.

실리콘 카바이드 에피 택셜 웨이퍼가 필요한 이유는 무엇입니까?