SiCのエピタキシー

- 説明

製品の説明

SiCのエピタキシー

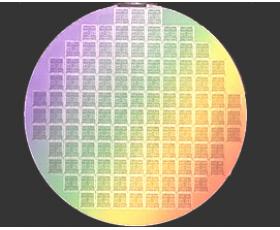

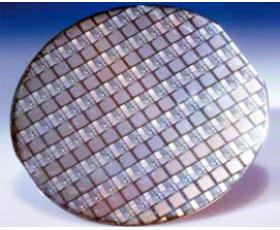

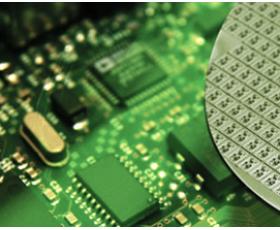

PAM-XIAMEN provide custom thin film (silicon carbide) SiC epitaxy on 6H or 4H substrates for the development of silicon carbide devices. SiC epi wafer is mainly used for the fabrication of 600V~3300V power devices, including SBD, JBS, PIN, MOSFET, JFET, BJT, GTO, IGBT, etc. With a silicon carbide wafer as a substrate, a chemical vapor deposition (CVD) method is usually used to deposit a layer of single crystal on the wafer to form an epitaxial wafer. Among them, SiC epitaxy are prepared by growing silicon carbide epitaxial layers on conductive silicon carbide substrates, which can be further fabricated into power devices.

1.SiCエピタキシーの仕様:

| アイテム | 仕様 | 標準値 |

| ポリタイプ | 4H | — |

| オフの方向に向けて | 4度オフ | — |

| <11 2_ 0> | ||

| 導電率 | n型 | — |

| ドーパント | 窒素 | — |

| キャリア濃度 | 5E15-2E18 cm-3 | — |

| 公差 | ±25% | ±15% |

| 均一 | 2” (50.8ミリメートル)<10% | 7% |

| 3” (76.2ミリメートル)<20% | 10% | |

| 4” (100ミリメートル)<20% | 15% | |

| 厚さの範囲 | 5-15ミクロン | — |

| 公差 | ±10% | ±5% |

| 均一 | 2” <5% | 2% |

| 3” <7% | 3% | |

| 4” <10% | 5% | |

| 大きな点欠陥 | 2” <30 | 2” <15 |

| 3” <60 | 3” <30 | |

| 4” <90 | 4” <45 | |

| エピ欠陥 | ≤20cm-2 | ≤10cm-2 |

| ステップバンチング | ≤2.0nmさ(Rq) | ≤1.0nmさ(Rq) |

| (粗さ) |

50.8および76.2mmの場合は2mmのエッジ除外、100.0mmの場合は3mmのエッジ除外注:

•厚さとキャリア濃度のすべての測定ポイントの平均(5ページを参照)

•20ミクロン未満のN型エピ層の前には、n型、1E18、0.5ミクロンのバッファー層があります。

•すべてのドーピング密度がすべての厚さで利用できるわけではありません

•均一性:標準偏差(σ)/平均

•エピパラメータに関する特別な要件はリクエストに応じて提供されます

2. Introduction of SiC Epitaxy

なぜ炭化ケイ素エピタキシャルウェーハが必要なのですか? Because different from the traditional silicon power device manufacturing process, silicon carbide power devices cannot be directly fabricated on silicon carbide single crystal materials. High-quality epitaxial materials must be grown on conductive single crystal substrates, and various devices manufactured on the SiC epitaxial wafer.

The main epitaxial technology for SiC epitaxy growth is chemical vapor deposition (CVD), which realizes a certain thickness and doped silicon carbide epitaxial material through the growth of SiC epitaxy reactor step flow. With the improvement of silicon carbide power device manufacturing requirements and withstand voltage levels, SiC epi wafer continues to develop in the direction of low defects and thick epitaxy.

In recent years, the quality of thin silicon carbide epitaxial materials (<20 μm) has been continuously improved. The microtubule defects in the epitaxial materials have been eliminated. However, the SiC epitaxy defects, such as drop, triangle, carrot, screw dislocation, basal plane dislocation, deep-level defects, etc., become the main factor affecting device performance. With the advancement of SiC epitaxy process, the thickness of the epitaxial layer has developed from a few μm and tens of μm in the past to the current tens of μm and hundreds of μm. Thanks to the advantages of SiC over Si, the SiC epitaxy market is growing rapidly.

Since silicon carbide devices must be fabricated on epitaxial materials, basically all silicon carbide single crystal materials will be used as SiC epitaxial film to grow epitaxial materials. The technology of silicon carbide epitaxial materials has developed rapidly internationally, with the highest epitaxial thickness reaching more than 250 μm. Among them, the epitaxy technology of 20 μm and below has a high maturity. The surface defect density has been reduced to less than 1/cm2, and the dislocation density has been reduced from 105/cm2 to 103/cm2. The dislocation conversion rate of base plane is close to 100%, which has basically met the requirements of epitaxial materials for large-scale production of silicon carbide devices.

In recent years, the international 30 μm~50 μm epitaxial material technology has also matured rapidly, but due to the limitation of SiC epi market demand, the progress of industrialization has been slow. At present, industrialization company can offer silicon carbide epitaxial materials in batches, include Cree SiC epitaxy, PAM-XIAMEN SiC epitaxy, Dow Corning SiC epitaxy etc..

3.Test Methods

1番。 キャリア濃度ネットドーピングを水銀プローブCVを用いてのafer全体の平均値として決定されます。

第2号。 厚さ:厚さは、FTIRを用いてウエハ全体の平均値として決定されます。

No.3.Large点欠陥:顕微鏡検査は、オリンパス光学顕微鏡で、100倍で行われ、または同等の。

No.4。 Epi DefectsInspectionまたはKLA-TencorCandela CS20 Optical SurfaceAnalyzerまたはSICAで実行される欠陥マップ。

第5号。 ステップバンチング:ステップバンチングと粗さは10μMのx10μm領域にAFM(原子間力顕微鏡)によってscanedれます

3-1:Large Point Defects Descriptions

肉眼に明確な形状を示し、ある欠陥>全体50microns。 これらの機能は、スパイク、付着粒子、チップandcratersが含まれます。 大きい点欠陥3mm未満で離れつの欠陥としてカウント。

3-2:Epitaxy Defect Descriptions

SiC epitaxy defects include 3C inclusions, comet tails, carrots, particles, silicon droplets and downfall.

4. Application of SiC epitaxial wafer

力率補正(PFC)

PVインバータやUPS(無停電電源装置)インバータ

モータードライブ

出力整流

ハイブリッドや電気自動車

600V、650V、1200V、1700V、3300VとSiCショットキー・ダイオードが使用可能です。

以下の分野別の詳細アプリケーションをご覧ください。

| フィールド | 無線周波数(RF) | パワーデバイス | LED |

| 材料 | SiLDMOS | シ | GaN / Al2O3 |

| GaAsの | GaN / Si | GaN / Si | |

| GaN / SiC | SiC / SiC | GaN / SiC | |

| GaN / Si | Ga203 | / | |

| デバイス | SiCベースのGaN HEMT | SiCベースのMOSFET SiCベースのBJT SiCベースのIGBT SiCベースのSBD |

/ |

| アプリケーション | レーダー、5G | 電気自動車 | ソリッドステート照明 |

5. Mechanical wafers with Epi layes: are available, such as for process monitoring, which require wafers with low bow and warpage.

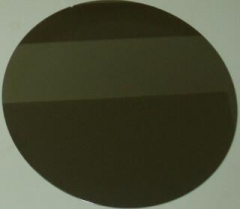

Intrinsic SiC Epilayer on Silicon carbide substrate