PAM-XIAMEN offre GaN su wafer HEMT di silicio per Power, E-mode. Poiché la caratteristica normalmente attiva aumenterà la complessità della progettazione del circuito e del consumo energetico, la progettazione di un HEMT avanzato (E-Mode) che viene disattivato con polarizzazione di griglia zero sarà fondamentale per far avanzare l'applicazione di GaN-on-Silicon HEMT nel campo di potenza.

1. Strutture di E-MODEGaN HEMTsu substrato di silicio

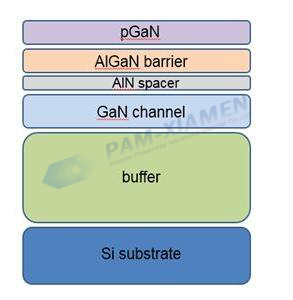

No. 1 GaN su struttura HEMT epitassiale di silicio

| GaN su dimensione dell'epitassia HEMT di silicio | 2″, 4″, 6″,8″ |

| / GaN HEMT struttura AlGaN | Fare riferimento 1.2 |

| Densità residua 2DEG (Vg=0 V) | <1e18/cm3 |

| AFM RMS (nm) di 5x5um2 | <0,25 nm |

| Inchino (um) | <=30um |

| Esclusione del bordo | <5mm |

| p-GaN | / |

| Strato del cappuccio in u-GaN | / |

| Al composizione | 20-30% |

| Strato barriera AlGaN | / |

| canale GaN | / |

| Tampone AlGaN | / |

| Materiale del substrato | Substrato di silicio |

| Spessore del wafer di Si (μm) | 675um(2″), 1000um(4″), 1300um(6″), 1500um(8″) |

N. 2 4 pollici GaN/Si Epi-Wafer PAM200211-HEMT

| GaN / Si HEMT Struttura Epi | ||

| Strato | Materiale | Spessore |

| 6 | p-GaN, drogato con Mg | – |

| 5 | AIN | – |

| 4 | AlGaN | – |

| 3 | AIN | – |

| 2 | GaN (strato canale) | – |

| 1 | Tampone (Al,Ga)N | > = 4 um |

| Substrato | Si (111), spessore 1000 +/- 25 um, deflessione <10 um | |

Nota:

1/ Allo stato attuale, la nostra struttura standard AlGaN 12NM, 25% Al ha il parametro corrispondente concentrazione portante > 6e12, mobilità > 2000, RS ~ 500, molto meglio;

2/ L'attuale concentrazione di drogante Mg è ~ 2e19 e la concentrazione di attivazione è ~ 4e17.

Caratteristiche di GaN su Si Epiwafer per l'alimentazione:

Elevata uniformità e buona ripetibilità;

Bassa corrente di dispersione con eccellente;

proprietà di trasporto 2DEG;

Tensione di rottura ≥ 650 V;

A norma RoHS

Applicazioni tipiche degli Epiwafer GaN a base di Si:

Adatto per HEMT di potenza e processo CMOS a basso costo;

Adatto per diodi di potenza

2. Che cos'è il GaN in modalità E su Silicon HEMT?

La modifica della struttura del processo del gate HEMT GaN su silicio per commutare la polarità della tensione di soglia può produrre un dispositivo HEMT GaN avanzato (tipo E). Lo scopo della modifica della struttura del processo è di esaurire il 2° sotto la porta con la condizione di nessuna tensione applicata, in modo che la tensione di soglia diretta possa essere aumentata dal 2° per formare un canale. Il gate GaN drogato con P è una struttura simile a un diodo nella struttura del gate e la tensione di soglia viene aumentata dalla caduta di tensione del diodo.

Attualmente, esistono tre metodi principali per utilizzare il gate di tipo p per realizzare HEMT in modalità avanzata basata su GaN:

- Il primo metodo di gate di tipo p consiste principalmente nell'utilizzare l'intero strato di tipo p epitassiale sullo strato barriera, quindi incidere e mantenere lo strato di tipo p sotto il gate per realizzare il miglioramento;

- Il secondo è tagliare lo strato epitassiale di tipo p, quindi mantenere lo strato di tipo p sotto il gate e incidere la maggior parte dello strato di tipo p nell'area non-gate, lasciando 5-20 nanometri dello strato di tipo p . Durante il processo di incisione, il plasma danneggerà l'interfaccia e influirà sulla stabilità del GaN sul dispositivo di alimentazione al silicio;

- Il terzo metodo di gate di tipo p consiste nell'eseguire l'epitassia secondaria nell'area del gate sullo strato barriera per far crescere il gate di tipo p.

3. Domande frequenti su GaN su Si Wafer for Power, E-mode

Q1:A proposito dei trattamenti superficiali per E-mode GaN su wafer Si HEMT: ci daresti anche qualche spunto per superare questo difficile problema? Soprattutto il processo di gate è nelle nostre menti. Non siamo molto sicuri dei trattamenti prima dell'evaporazione del gate metal.

A:Per quanto riguarda la superficie di GaN su wafer Si HEMT, i trattamenti organici sono importanti dopo l'incisione del pGaN, per riparare la superficie incisa.

Q2:Per la struttura dell'epi GaN su Si per HEMT in modalità E, abbiamo anche eseguito alcune simulazioni e ottenuto risultati simili nelle simulazioni. Voglio dire, 13 nm di barriera AlGaN andranno bene per il valore V° previsto. Si possono ottenere 180 mA/mm ma a quale distanza DS si osserva questa densità di corrente?

Secondo le nostre simulazioni, la riduzione dello spessore di AlGaN a 13 nm è buona, ma per essere sicuri dobbiamo anche mantenere la frazione molare di Al a 0,18. Hai qualche previsione su quanto questo cambierà l'IDSS?

A:La nostra distanza dalla sorgente al drenaggio è di circa 25 μm in base alla struttura epitassiale HEMT. Per quanto riguarda l'Idss della barriera GaN di 13 nm Al(0,18) è difficile da dire, poiché è anche influenzato dall'accuratezza dell'incisione. Per riferimento, abbiamo lavorato su un dispositivo con barriera GaN da 12 nm Al(0,15), l'Idss è ~72 mA/ mm.

Q3:Per quanto riguarda i dispositivi basati su GaN-on-Si con la tensione di soglia, abbiamo provato diversi metalli di gate (Pd, tungsteno, Ni, NiAu, Ti, ecc.) ma è sempre 0,7V. Dobbiamo aumentarlo fino a 1.2V hai anche qualche consiglio su questo problema? La tua guida aiuterà troppo.

A:Per quanto riguarda la tensione di rottura (BV): i wafer con la stessa struttura epi-simile di GaN/Si HEMT vengono sempre elaborati nella nostra fabbrica e si ottiene un'uscita BV stabile, con BV >650 V (Ids corrente di dispersione < 1 μA) . Un BV più elevato dovrebbe essere ottenuto mediante trattamenti superficiali adeguati e uno strato di passivazione ottimizzato.

Q4:Stiamo pensando di modificare lo spessore AlGaN della struttura GaN HEMT per aumentare il Vth. Cosa ne pensi? O forse puoi suggerire altre cose per aumentare il V.

A:Per quanto riguarda la tensione di soglia Vth del wafer E-mode GaN/Si HEMT: Riteniamo che la Vth possa essere migliorata riducendo lo spessore della barriera. Possiamo ottenere facilmente dispositivi con Vth >1,5 V nella nostra fabbrica, con una barriera Al0.2Ga0.8N di ~13 nm, mentre è ancora possibile mantenere una corrente di stato relativamente alta (>180 mA/mm). Nel tuo caso, la barriera AlGaN è un po' più spessa (18 nm), il che potrebbe limitare i valori V° a < 1 V.

Q5:Abbiamo bisogno di qualche tipo di attivazione per il doping Mg o hai già attivato il doping in wafer HEMT di GaN su Si?

A:Abbiamo già attivato il doping nel wafer GaN-on-Si HEMT.

Q6:Stiamo ancora lavorando per ottimizzare il processo sul tuo wafer. Finora siamo stati in grado di ottenere una rottura di 420 V con il wafer in modalità PGaN E.

Qual è la tua stima sulla tensione di rottura? Quanto in alto possiamo andare? Ricordo che mi hai detto che 650V potrebbero essere un po' difficili con la modalità E.

Nel frattempo hai qualche progresso sulla crescita dell'epi? È possibile acquistare un wafer in modalità D con guasto a 650 V?

A:La tensione di rottura può raggiungere i 1000 V sia per il wafer HEMT in modalità D che in modalità E.

Q7:Ricordo che la rottura verticale può arrivare fino a 1000V e abbiamo anche misurato circa 900V con uno dei campioni. Per il funzionamento a 600v hai suggerito la modalità D. Comprendo che la modalità E non sarà in grado di raggiungere quel valore. Mi sbaglio? Hai qualche suggerimento per noi per raggiungere 600V con wafer in modalità E?

A:Nel funzionamento a 600 V, suggeriamo di utilizzare il wafer HEMT in modalità D, che è più adatto a questa tensione, ma ciò non significa che la tensione di rottura raggiunga solo 600 V, come accennato, entrambi possono arrivare a 1000 V.

Q8:Attualmente stiamo lavorando per migliorare la tensione di rottura dei dispositivi con il tuo GaN su wafer Si HEMT. Abbiamo ottenuto ~350V ma stiamo cercando il modo di ridurre le perdite per migliorare il guasto. Ma nel frattempo abbiamo problemi con la tensione di soglia. Dobbiamo avere più tensioni positive. Ho bisogno del tuo aiuto e dei tuoi suggerimenti per migliorare i risultati.

Quello che ho in mente è di diminuire un po' lo spessore della barriera di AlGaN ma compensando la perdita di Ns aumentando un po' la composizione di Al. A nostro avviso questo dovrebbe migliorare la tensione di soglia dei dispositivi. Cosa ne pensi? Possiamo ordinare un altro wafer per migliorare questi parametri.

Hai qualche suggerimento per migliorare la tensione di rottura del dispositivo?

A: RE: la tensione di rottura dei dispositivi HEMT su wafer GaN/Si:

Il wafer che vi abbiamo consegnato si basa sul nostro buffer HV, che ha una tensione di rottura verticale > 1000 V (@I < 1 uA/ mm2).

In realtà, secondo i dispositivi fabbricati su questa struttura epi, nel nostro stabilimento, la perdita di stato off è Ids< 0,1 uA/ mm, mentre Vds = 650 V (Lds=15 um).

Sia il buffer epi che il processo del chip contribuiscono alla perdita, quindi ti consigliamo di controllare il processo del chip, in particolare lo strato di passivazione, che è anche critico per la perdita.

RE: il V° dei dispositivi su GaN su wafer HEMT di silicio:

Uno strato barriera più sottile aiuterà sicuramente ad aumentare il Vth.

possiamo ridurre lo spessore di AlGaN (20% Al) a 12,5 nm per te (il precedente era ~ 18 nm).

Un Vth> 2 V (@Ids~10 uA/ mm) è stato dimostrato nel nostro fab, basato su questa struttura.

Sebbene sacrificherà la Rs, si ottiene un valore Rs di ~550 ohm/sq.

A proposito, anche il processo del truciolo, in particolare il materiale del cancello, è importante per Vth.

Q9:Apprezzo la tua risposta. Grazie. Non abbiamo problemi con la rottura verticale, misuriamo anche circa 1kV. Ma la perdita DS (usiamo LDS12um) è maggiore e non possiamo raggiungere 650V.

A mia osservazione il nostro problema principale deriva dalla perdita del cancello. E come hai affermato, il materiale del cancello influisce su questa perdita. Usiamo Ni/Au come gate metal. Ma la tua piccola guida sarà molto apprezzata. Quale potrebbe essere il tuo suggerimento per migliorare la perdita del gate e anche il Vth? Usi ALD o dielettrico simile sotto il cancello metallico? Quale struttura metallica usi? Che tipo di cose mi consigliate per migliorare il contatto del cancello?

A:RIF:il metallo del cancello per la fabbricazione del dispositivo GaN HEMT:

La nostra linea di produzione è priva di "Au", quindi non viene utilizzato Au e inoltre, il contatto Ni/Au di solito fornisce elevate perdite di gate.

Tre tipi di contatto del gate possono migliorare Vth: Ni, W (wolfram) o TiN (la nostra opzione).

Per quanto riguarda la perdita:

Misuriamo la dispersione dello stato off a Vg = 0 V.

In realtà, dipende dal Vth, se il tuo Vth è vicino a 0 V, la perdita a Vg=0V è alta, in quanto il dispositivo non è completamente "spento"; se Vth > 1,5 V, il nostro dispositivo fornisce una bassa dispersione (sub uA) @ Vg = 0 V.

Si prega di prestare attenzione ai difetti di incisione, che possono anche contribuire alla perdita di stato off.

Ci auguriamo che le informazioni di cui sopra possano aiutare.

Q10: I would like to insert an 1 nm AlN layer between p-GaN and AlGaN. Is it possible?

A: No problem to inser an 1nm AlN layer between p-GaN and AlGaN, but which can not help to stop etch.

Per ulteriori informazioni, si prega di contattarci e-mail avictorchan@powerwaywafer.com e powerwaymaterial@gmail.com.