Bạn có thể mua wafer silicon epi từ PAM-XIAMEN,một nhà cung cấp wafer epiticularbạn muốn tìm, nơi có thể cung cấp wafer silicon epi hoặc wafer silicon epi tùy chỉnh. Kích thước chúng tôi có thể cung cấp là 2”, 4”, 5”, 6” hoặc 8”. Thông tin chi tiết xin vui lòng xem danh sách wafer của Si epi wafer như sau:

![]()

1. Danh sách wafer của wafer silicon Epitaxy

| wafer số | Kích thước | Loại | Độ dày (um) | Chống lại (Ohm.cm) | EPI (Loại) | Độ dày EPI(μm) | Chống lại EPI(Ohm.cm) | Số lượng (chiếc) |

| PAM-XIAMEN-WAFER-#E3 | 4" | P111 | 500 ± 15 | — | P111 | 14,5-16,5um | 6.5-7.5 | 34 |

| PAM-XIAMEN-WAFER-#E4 | 4" | P111 | 500 ± 15 | — | P111 | 11-13um | 3-3.6 | 33 |

| PAM-XIAMEN-WAFER-#E5 | 4" | P111 | 500 ± 15 | — | P111 | 15 ± 1,5um | 2,5 ± 0,25 | 19 |

| PAM-XIAMEN-WAFER-#E6 | 4" | P111 | 500 ± 15 | — | P111 | 15 ± 1um | 5,5 ± 0,5 | 20 |

| PAM-XIAMEN-WAFER-#E7 | 2 " | GaAs Epi Wafer | 350um | Điện áp 1-10,Độ sáng 100-115 | Bước sóng 600-607 | 1.8-2.2 | — | 8 |

| PAM-XIAMEN-WAFER-#E8 | 2 " | Bánh xốp GaN Epi | Chất nền Sapphire 430um | — | — | Lớp Epi 4,7-9,1um | — | 2 |

| PAM-XIAMEN-WAFER-#E9 | 6 " | P100 | 400 ± 10 | 8-12 | N100 | 20±10% | 3.0-5.0 | 50 |

| PAM-XIAMEN-WAFER-#E10 | 5 " | P100 | 525 ± 15 | — | P100 | 21 | <24 | 10 |

| PAM-XIAMEN-WAFER-#E11 | 5 " | N100 | 625±15 | 0.001-0.005 | N100 | 8,5 ± 0,51 | 0,9 ± 0,05 | 13 |

| PAM-XIAMEN-WAFER-#E12 | 5 " | P100 | 525 ± 15 | 0.005-0.020 | P100 | 36-44 | 30-44 | 15 |

| PAM-XIAMEN-WAFER-#E13 | 5 " | N100 | 525 ± 15 | — | N100 | 21 | 60 | 5 |

2. Wafer Silicon Epitaxy là gì?

Tấm silicon epi được phát triển lần đầu tiên vào khoảng năm 1966 và được chấp nhận thương mại vào đầu những năm 1980.[5] Các phương pháp trồnglớp epiticular trên silicon đơn tinh thểhoặc các tấm mỏng khác bao gồm: nhiều loại lắng đọng hơi hóa học (CVD) được phân loại là CVD áp suất khí quyển (APCVD) hoặc lắng đọng hơi hóa học hữu cơ kim loại (MOCVD), cũng như epitaxy chùm phân tử (MBE). Hai phương pháp “kerfless” (không cưa mài mòn) để tách lớp epitaxy khỏi chất nền được gọi là “cắt implant” và “xả ứng suất”. Một phương pháp có thể áp dụng khi lớp epi và chất nền là cùng một vật liệu sử dụng phương pháp cấy ion để lắng đọng một lớp nguyên tử tạp chất tinh thể mỏng và tạo ra ứng suất cơ học ở độ sâu chính xác của độ dày lớp epi dự kiến. Ứng suất cục bộ gây ra cung cấp một đường dẫn được kiểm soát để lan truyền vết nứt trong bước phân cắt tiếp theo.[7] Trong quy trình loại bỏ ứng suất khô áp dụng khi lớp epi và chất nền là những vật liệu khác nhau phù hợp, vết nứt được kiểm soát được tạo ra bởi sự thay đổi nhiệt độ ở giao diện epi/wafer hoàn toàn do ứng suất nhiệt do sự không phù hợp trong quá trình giãn nở nhiệt giữa lớp lớp epi và chất nền, mà không cần bất kỳ lực cơ học hoặc công cụ bên ngoài nào để hỗ trợ sự lan truyền vết nứt. Theo báo cáo, quy trình này tạo ra sự phân cắt mặt phẳng nguyên tử đơn lẻ, giảm nhu cầu đánh bóng sau khi nhấc ra và cho phép tái sử dụng nhiều lần chất nền lên đến 10 lần.

3. Phương pháp tiêu chuẩn để kiểm tra độ dày và sự thay đổi tổng độ dày của wafer silicon Epi

Có hai phương pháp chính để kiểm tra sự thay đổi độ dày và tổng độ dày của silicon epitaxy trong ngành, bao gồm phép đo điểm rời rạc và phép đo quét.

3.1 Kiểm tra độ dày của wafer Si Epi bằng phép đo điểm rời rạc

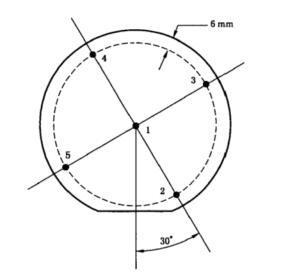

Độ dày của tấm wafer epiticular silicon được đo tại điểm chính giữa của tấm wafer silicon và tại 4 điểm đối xứng trên chu vi 6 mm tính từ mép của tấm wafer silicon. Hai trong số các điểm nằm trên đường kính 30° theo hướng ngược chiều kim đồng hồ của đường phân giác vuông góc với mặt phẳng tham chiếu chính của tấm đệm silicon và hai điểm còn lại nằm trên một đường kính khác vuông góc với đường kính (xem Hình 1). Điểm trung tâm của wafer silicon epi. Độ dày được coi là độ dày danh nghĩa của wafer silicon epiticular. Sự khác biệt giữa độ dày tối đa và độ dày tối thiểu trong số năm phép đo độ dày được gọi là tổng độ biến thiên độ dày của wafer silicon.

Hình 1 Vị trí điểm đo

3.2 Quét để đo TTV của wafer Silicon Epi

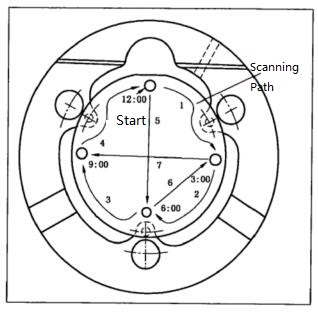

Tấm wafer silicon được hỗ trợ bởi ba đỉnh hình bán cầu trên vòng tham chiếu và độ dày được đo tại điểm trung tâm của tấm wafer silicon epi. Giá trị đo được là độ dày danh nghĩa của wafer Si. Sau đó quét bề mặt của Si epitaxy theo mẫu quy định để đo độ dày và chỉ báo tự động hiển thị tổng biến thể độ dày. Sơ đồ đường dẫn quét được hiển thị trong Hình 2.

Hình 2 Đường quét

3.3 Can thiệp để đo Si Epi wafer TTV

Đối với phép đo điểm rời rạc, tổng độ biến thiên độ dày của phép đo điểm rời rạc chỉ dựa trên dữ liệu đo của 5 điểm, không thể phát hiện ra những thay đổi hình học bất thường của các bộ phận khác trên lớp epitaxy wafer silicon. Một sự thay đổi cục bộ của một điểm nhất định trên tấm bán dẫn silicon có thể dẫn đến kết quả sai. Sự thay đổi cục bộ này có thể bắt nguồn từ các khuyết tật bề mặt như sứt mẻ, nhiễm bẩn, gò đồi, hố, vết dao, gợn sóng, v.v.

Đối với phép đo quét, trong quá trình quét, bất kỳ thay đổi nào trong mặt phẳng tham chiếu sẽ gây ra lỗi trong giá trị chỉ báo phép đo, tương đương với độ lệch của giá trị vectơ trục của chênh lệch giữa giá trị tối đa và tối thiểu trên trục đầu dò . Nếu thay đổi này xảy ra, nó có thể dẫn đến việc tính toán các giá trị cực trị tại các vị trí không chính xác. Tính không song song của mặt phẳng tham chiếu và mặt phẳng chuẩn granit cũng sẽ gây ra lỗi của giá trị thử nghiệm. Ngoài ra, các hạt lạ và ô nhiễm giữa vòng tham chiếu và nền tảng đá granit sẽ gây ra lỗi.

Để biết thêm thông tin, vui lòng liên hệ với chúng tôi qua email victorchan@powerwaywafer.com và powerwaymaterial@gmail.com.